Page 146 - 《真空与低温》2025年第3期

P. 146

仲子琪等:芯片级原子束钟真空腔技术研究 417

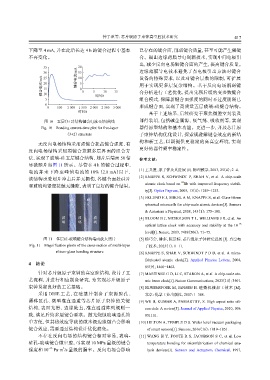

下降至 4 mA,并在此后长达 4 h 的键合过程中基本 已存在的键合面,削弱键合质量,甚至可能产生解键

不再变化。 合。提出边缘薄膜导电创新技术,实现中间电极引

出,减少反向电场解键合面的产生,提高键合质量。

35 20

30 键合电流/mA 15 边缘薄膜导电技术避免了点电极引出方法对键合

键合电流/mA 20 5 0 0 5 10 15 用于实现更多层复杂结构。基于反向电场削弱键

设备的特殊要求,以及对键合层数的限制,可扩展

25

10

15

合分析进行工艺优化,提出先强后缓的变参数键合

10

5 时间/t 组合模式,保障新键合面强度的同时不过度削弱已

0 形成键合面,实现了高质量五层玻璃-硅键合结构。

0 500 1 000 1 500 2 000 2 500 3 000

时间/t

基于上述结果,后续研究于聚焦微腔室封装及

图 10 五层(3+2)结构键合电流-时间曲线 部件装填,包括碱金属源、吸气剂、吸收剂等,实现

Fig. 10 Bonding current-time plot for five-layer 器件原型结构和基本功能。更进一步,开展芯片原

(3+2) structure 子束钟结构优化设计,探索规避解键合效应的新结

构和新工艺,以期提供更稳定的高真空环境,实现

无反向电场结构采用强键合提高键合强度,有

更好的器件频率稳定性。

反向电场结构采用弱键合兼顾多层界面的组合方

法,实现了玻璃-硅五层键合结构,划片后端面 50 倍 参考文献:

显微照片如图 11 所示。尽管在 4 h 的键合过程中,

电流并未下降至峰值电流的 10% (2.8 mA)以下, [1] 王义遒. 原子钟及其进展 [J]. 物理教学,2003,25(4):2−4.

该结构承受划片冲击后并无损伤,各键合面处硅片 [2] KNAPPE S, SCHWINDT P, SHAH V, et al. A chip-scale

87

和玻璃均紧密接触无缝隙,表明了良好的键合结果。 atomic clock based on Rb with improved frequency stabili-

ty[J]. Optics Express,2005,13(4):1249−1253.

[3] EKLUND E J,SHKEL A M,KNAPPE S,et al. Glass-blown

硅 硅

片 片 spherical microcells for chip-scale atomic devices[J]. Sensors

& Actuators a Physical,2008,143(1):175−180.

玻 玻 玻 [4] BLOOM B J,NICHOLSON T L,WILLIAMS J R,et al. An

璃 璃 璃

optical lattice clock with accuracy and stability at the 10 −18

level[J]. Nature,2013,7488(506):71−75.

图 11 多层硅-玻璃键合结构端面放大照片 [5] 杨巧会,潘多,陈景标. 芯片级原子钟研究进展 [J]. 真空电

Fig. 11 Magnification photo of the cross-section of multi-layer 子技术,2023(1):1−11.

silicon-glass bonding structure

[6] KNAPPE S,SHAH V,SCHWINDT P D D,et al. A micro-

fabricated atomic clock[J]. Applied Physics Letters, 2004,

4 结论

85(9):1460−1462.

针对芯片级原子束钟的真空腔结构,设计了工 [7] MARTINEZ G D,LI C,STARON A,et al. A chip-scale ato-

艺流程,并进行相应制备研究,为实现芯片级原子 mic beam clock[J]. Nature Communications,2023(14):3501.

束钟奠定良好的工艺基础。 [8] ELWENSPOEK M,JANSEN H. 硅微机械加工技术 [M].

采用 DRIE 工艺,在硅基片制备了束源腔孔、 北京:化学工业出版社,2007:1−348.

漂移区孔、微型准直通道等芯片原子束钟的关键 [9] WU B,KUMAR A,PAMARTHY,S. High aspect ratio sili-

结构,表面光滑、边缘陡直,准直通道阵列规则一 con etch:A review[J]. Journal of Applied Physics,2010,108:

致,满足后续多层键合要求。激光烧蚀玻璃通孔简 051101.

单方便,但其热效应导致的微米级边缘微凸会影响 [10] HILTON A,TEMPLE D S. Wafer level vacuum packaging

键合效应,需要通过结构设计优化避免。 of smart sensors[J]. Sensors,2016(16):1819−1851.

不存在反向电场的结构键合相对容易,玻璃- [11] WANG H Y, FOOTE R S, JACOBSON S C, et al. Low

硅孔-玻璃键合微空腔,可实现 10 MPa 量级的键合 temperature bonding for microfabrication of chemical ana-

3

−13

强度和 10 Pa·m /s 量级的漏率。反向电场会影响 lysis devices[J]. Sensors and Actuators: Chemical, 1997,