Page 336 - 《软件学报》2021年第12期

P. 336

4000 Journal of Software 软件学报 Vol.32, No.12, December 2021

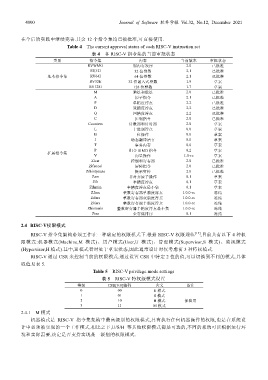

在今后的实践中继续完善.其余 12 个指令集均已被批准,可直接使用.

Table 4 The current approval status of each RISC-V instruction set

表 4 各 RISC-V 指令集的当前审批状态

类别 指令集 内容 当前版本 审批状态

RVWMO 弱内存次序 2.0 已批准

RV32I 32 位整数 2.1 已批准

基本指令集 RV64I 64 位整数 2.1 已批准

RV32E 32 位嵌入式整数 1.9 草案

RV128I 128 位整数 1.7 草案

M 乘法和除法 2.0 已批准

A 原子指令 2.1 已批准

F 单精度浮点 2.2 已批准

D 双精度浮点 2.2 已批准

Q 四精度浮点 2.2 已批准

C 压缩指令 2.0 已批准

Counters 计数器和计时器 2.0 草案

L 十进制浮点 0.0 草案

B 位操作 0.0 草案

J 动态翻译语言 0.0 草案

T 事务内存 0.0 草案

P 组合 SIMD 指令 0.2 草案

扩展指令集

V 向量操作 1.0-rc 草案

Zicsr 控制和寄存器 2.0 已批准

Zifencei 屏障指令 2.0 已批准

Zihintpause 提示暂停 2.0 已批准

Zam 非对齐原子操作 0.1 草案

Zfh 半精度浮点 0.1 草案

Zfhmin 半精度浮点最小集 0.1 草案

Zfinx 整数寄存器单精度浮点 1.0.0-rc 冻结

Zdinx 整数寄存器双精度浮点 1.0.0-rc 冻结

Zhinx 整数寄存器半精度浮点 1.0.0-rc 冻结

Zhinxmin 整数寄存器半精度浮点最小集 1.0.0-rc 冻结

Ztso 全存储排序 0.1 冻结

2.4 RISC-V权限模式

RISC-V 指令集架构必须工作在一种确定的权限模式下.根据 RISC-V 权限规范 [12] ,目前共有以下 4 种权

限模式:机器模式(Machine,M 模式)、用户模式(User,U 模式)、管理模式(Supervisor,S 模式)、监视模式

(Hypervisor,H 模式).其中,H 模式暂时处于草案状态,因此通常设计时仅考虑前 3 种特权模式.

RISC-V 通过 CSR 来控制当前的权限模式.通过设置 CSR 中特定 2 位的值,可以切换到不同的模式.具体

取值见表 5.

Table 5 RISC-V privilege mode settings

表 5 RISC-V 特权级模式设置

等级 CSR[9:8]编码 含义 备注

0 00 U 模式

1 01 S 模式

2 10 H 模式 保留用

3 11 M 模式

2.4.1 M 模式

机器模式是 RISC-V 指令集架构中最高级别的权限模式,具有执行任何机器操作的权限,也是在系统设

计中必须被实现的一个工作模式.相比之下,U/S/H 等其他权限模式都是可选的,不同的系统可以根据运行环

境和实际需要,决定是否支持实现某一级别的权限模式.