Page 331 - 《软件学报》2021年第12期

P. 331

刘畅 等:RISC-V 指令集架构研究综述 3995

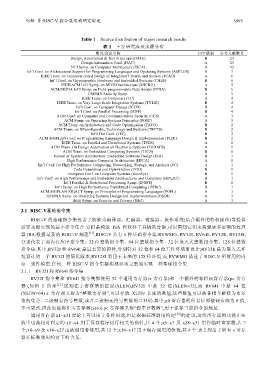

Table 1 Source distribution of major research results

表 1 主要研究成果来源分布

期刊/会议名称 CCF 级别 参考文献数目

Design, Automation & Test in Europe (DATE) B 23

Design Automation Conf. (DAC) A 13

Int’l Symp. on Computer Architecture (ISCA) A 12

Int’l Conf. on Architectural Support for Programming Languages and Operating Systems (ASPLOS) A 7

IEEE Trans. on Computer-aided Design of Integrated Circuits and System (TCAD) A 6

Int’l Conf. on Cryptographic Hardware and Embedded Systems (CHES) B 6

IEEE/ACM Int’l Symp. on MICROarchitecture (MICRO) A 5

ACM/SIGDA Int’l Symp. on Field-programmable Gate Arrays (FPGA) B 5

USENIX Security Symp. A 5

IEEE Trans. on Computers (TC) A 4

IEEE Trans. on Very Large Scale Integration Systems (TVLSI) B 4

Int’l Conf. on Computer Design (ICCD) B 4

Int’l Conf. on Parallel Processing (ICPP) B 4

ACM Conf. on Computer and Communications Security (CCS) A 3

ACM Symp. on Operating Systems Principles (SOSP) A 3

ACM Trans. on Architecture and Code Optimization (TACO) B 2

ACM Trans. on REconfigurable Technology and Systems (TRETS) B 2

Int’l Test Conf. (ITC) B 2

ACM SIGPLAN Conf. on Programming Language Design & Implementation (PLDI) B 2

IEEE Trans. on Parallel and Distributed Systems (TPDS) A 1

ACM Trans. On Design Automation of Electronic Systems (TODAES) A 1

ACM Trans. on Embedded Computing Systems (TECS) B 1

Journal of Systems Architecture: Embedded Software Design (JSA) B 1

High Performance Computer Architecture (HPCA) A 1

Int’l Conf. for High Performance Computing, Networking, Storage, and Analysis (SC) A 1

Code Generation and Optimization (CGO) B 1

European Conf. on Computer Systems (EuroSys) B 1

Int’l Conf. on High Performance and Embedded Architectures and Compilers (HiPEAC) B 1

Int’l Parallel & Distributed Processing Symp. (IPDPS) B 1

Int’l Symp. on High Performance Distributed Computing (HPDC) B 1

ACM SIGPLAN-SIGACT Symp. on Principles of Programming Languages (POPL) A 1

USENIX Symp. on Operating Systems Design and Implementations (OSDI) A 1

IEEE Symp. on Security and Privacy (S&P) A 1

2.1 RISC-V基础指令集

RISC-V 的基础指令集包含了能够为编译器、汇编器、链接器、操作系统(结合额外的特权操作)等提供

必要功能实现的最小指令集合.它们是构筑 ISA 和软件工具链的骨架,可以围绕它们来构建更多定制的处理

器 ISA.根据最新的 RISC-V 规范 [11] ,RISC-V 共有 5 种基础指令集:RVWMO、RV32I、RV64I、RV32E、RV128I,

分别代表了弱内存次序指令集、32 位整数指令集、64 位整数指令集、32 位嵌入式整数指令集、128 位整数

指令集.其中,RV32I 和 RV64I 是最主要的两种,分别针对 32 位和 64 位工作环境而设计;RV32E 是为嵌入式环

境设计的一个 RV32I 的简化版本,RV128I 将用于未来的 128 位环境,而 RVWMO 描述了 RISC-V 所使用的内

存一致性模型.任何一种 RISC-V 指令集架构都必须完整地实现一种基础指令集.

2.1.1 RV32I 和 RV64I 指令集

RV32I 指令集和 RV64I 指令集都使用 32 个通用寄存器(x 寄存器)和一个额外的非特权寄存器(pc 寄存

器),如图 2 所示 [11] .区别在于寄存器的位宽(XLEN),RV32I 中是 32 位(XLEN=32),而 RV64I 中是 64 位

(XLEN=64).x 寄存器又称为“整数寄存器”,可以存放 XLEN 长度的数值,这些数值可以被各指令解释为布尔

值的集合、二进制有符号整数,或者二进制无符号整数的二补码.其中,x0 寄存器的所有位都被硬布线为 0 值,

不可更改,因此也被称作零寄存器(zero).pc 寄存器又称“程序计数器”,用于保存当前指令的地址.

通用寄存器 x1~x31 理论上可以用于各种用途,但是根据标准调用约定 [20] 的建议,这些寄存器的功能在实

践中也是相对固定的:x1~x4 用于保存程序运行相关的指针,共 4 个;x5~x7 及 x28~x31 用作临时寄存器,共 7

个;x8~x9 及 x18~x27 由被调用者使用,共 12 个;x10~x17 用于保存调用的参数,共 8 个.表 2 列出了所有 x 寄存

器在标准调用约定下的含义.