Page 333 - 《软件学报》2021年第12期

P. 333

刘畅 等:RISC-V 指令集架构研究综述 3997

计算结果的低 XLEN 位(即低 32 位)作为指令的执行结果,忽略计算溢出.RV64I 沿用了该指令,但寄存器和执行

结果都被扩展到 64 位.同时 RV64I 新增了 ADDIW 指令,用以产生 32 位的计算结果,再将其符号扩展至 64 位并

忽略计算溢出.

2.1.2 RV32E 指令集

RV32E 是专为嵌入式环境设计的指令集,是对 RV32I 指令集的一种简化.根据 RISC-V 规范 [11] 的描述,它

与 RV32I 唯一的区别在于,将可用的整数寄存器的数目从 32 减少到 16,即只使用 x0~x15 和 pc 完成所有的指

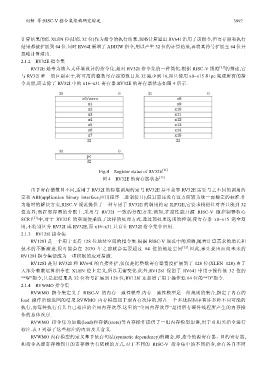

令功能,而去除了 RV32I 中的 x16~x31 寄存器.RV32E 的寄存器状态如图 4 所示.

Fig.4 Register status of RV32E [11]

图 4 RV32E 的寄存器状态 [11]

由于寄存器数目不同,适用于 RV32I 的标准调用约定与 RV32E 并不兼容.RV32E 需要与之不同的调用约

定和 ABI(application binary interface,应用程序二进制接口),但目前还没有这方面较为统一而稳定的标准.作

为临时的解决方案,RISC-V 规范提供了一种专用于 RV32E 的调用约定 ILP32E,它要求栈指针对齐只能到 32

位边界;而在寄存器的分配上,采用与 RV32I 一致的分配方案.例如,在高性能开源 RISC-V 微控制器核心

SCR1 [21] 中,对于 RV32E 的实现便采取了这样的处理方式.通过预处理选项的控制,使寄存器 x0~x15 完全复

用,不特别区分 RV32I 或 RV32E,而 x16~x31 只有在 RV32I 指令集中启用.

2.1.3 RV128I 指令集

RV128I 是一个用于支持 128 位地址空间的指令集.根据 RISC-V 规范中的预测,随着计算需求的增长和

技术的不断演进,很可能会在 2030 年之前就会需要超过 64 位的地址空间 [11] .因此,事先提出面向未来的

RV128I 指令集便成为一项积极的应对措施.

RV128I 是对 RV32I 和 RV64I 的直接外扩,仅仅是把整数寄存器宽度扩展到了 128 位(XLEN=128).由于

大部分整数运算指令在 XLEN 位上定义,所以无需变化.此外,RV128I 保留了 RV64I 中用于操作低 32 位的

“*W”指令,只是把结果从 32 位符号扩展到 128 位;RV128I 还新增了用于操作低 64 位的“*D”指令.

2.1.4 RVWMO 指令集

RVWMO 指令集定义了 RISC-V 的内存一致性模型.内存一致性模型是一组规则的集合,指定了内存的

load 操作所能返回的结果.RVWMO 内存模型属于弱内存次序的,即在一个多线程程序有许多种不同可能的

执行,而每种执行有其自己相应的全局内存次序.这里的“全局内存次序”是指所有硬件线程所产生的内存操

作的总体次序.

RVWMO 指令集为加载(load)和存储(store)等内存操作提供了一组内存模型原语,用于对相关指令进行

标注.表 3 列举了这些标注的内容及其含义.

RVWMO 内存模型的定义基于依存句法(syntactic dependency)的概念,即,指令的源寄存器、目的寄存器,

和指令从源寄存器到目的寄存器含有依赖的方式.对于不同的 RISC-V 指令集中的不同指令,会有各自不同