Page 340 - 《软件学报》2021年第12期

P. 340

4004 Journal of Software 软件学报 Vol.32, No.12, December 2021

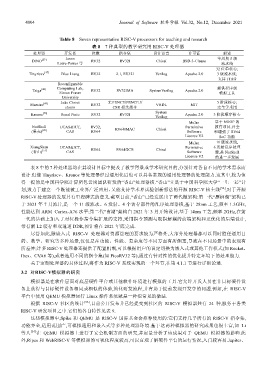

Table 8 Seven representative RISC-V processors for teaching and research

表 8 7 种典型的教学研究用 RISC-V 处理器

处理器 开发者 位数 指令集 设计语言 许可证 描述

Jason 单周期 5 级

[27]

DINO RV32 RV32I Chisel BSD-3-Clause

Lowe-Power 等 流水线

32 位单核心;

Tinyriscv [47] Blue Liang RV32 2.1, RV32I Verilog Apache 2.0 3 级流水线;

支持 JTAG

Reconfigurable

Taiga [48] Computing Lab, RV32 RV32IMA SystemVerilog Apache 2.0 提供程序级

Simon Fraser 模拟工具

University

Maestro [49] João Chrisó RV32 无 FENCE/FENCE.I/ VHDL MIT 5 阶段核心;

stomo CSR 相关指令 完全学术用

Kronos [50] Sonal Pinto RV32 RV32I System Apache 2.0 3 阶段顺序核心

Verilog

Mulan 基于 NOOP 的

NutShell UCAS&ICT, RV32, Permissive 教育项目,补全

(果壳) [28] CAS RV64 RV64IMAC Chisel Software 和增强了 RV64

License V2 SoC 功能

Mulan 11 级流水线,

XiangShan UCAS&ICT, RV64 RV64GCB Chisel Permissive 6 发射乱序处理

(香山) [51] CAS Software 器,是 NutShell

License V2 的进一步发展

表 8 中的 7 种处理器均在其设计目标中提及了教学背景或学术研究目的,分别针对各自不同的学术需求而

设计.但像 Tinyriscv、Kronos 等处理器经过通用化后也可以具备常规的通用处理器的处理能力.这其中,较为值

得一提的是中国科学院计算所包云岗团队研发的“香山”处理器核.“香山”立足于中国科学院大学“一生一芯”计

划,致力于建立一个既能被工业界广泛应用、又能支持学术界试验创新想法的开源 RISC-V 核主线 [52] ,对于开源

RISC-V 处理器的发展具有里程碑式的意义.截至目前,“香山”已经发展出了两代微架构:第一代“雁栖湖”架构已

于 2021 年 7 月流片,是一个 11 级流水、6 发射、4 个访存部件的乱序处理器核,基于 28nm 工艺,频率 1.3GHz,

性能达到 ARM Cortex-A76 水平;第二代“南湖”架构自 2021 年 3 月开始设计,基于 14nm 工艺,频率 2GHz,在前

一代的基础上加入了对位操作指令集扩展的支持,采用指令预测与取指解耦的前端架构和更优化的后端设计,

带有新 L2 缓存和双通道 DDR,预计将在 2021 年底完成.

尽管如此,除嵌入式 RISC-V 处理器对资源管理的要求较为严格外,大部分处理器都可以同时胜任通用目

的、教学、研究等多种场景,仅仅是在功能、性能、复杂度等不同方面有所侧重,导致在不同场景中的表现有

所差异;许多 RISC-V 处理器还提供了配置机制,可以根据用户的设定切换为嵌入式或其他工作模式(如 Rocket、

Ibex、CVA6 等),或者选用不同的指令集(如 PicoRV32 等),通过有针对性的优化提升特定环境下的处理能力.

关于定制处理器的具体过程,将作为 RISC-V 系统实现的一个环节,在第 4.1.1 节进行详细论述.

3.2 对RISC-V模拟器的研究

模拟器是在软件层面对底层硬件平台或其他软件环境进行模拟的工具.它允许开发人员在非目标硬件设

备上获得与目标硬件设备相同或相似的体验,简化研发流程,并有助于提前发现开发中的问题.例如,在 RISC-V

平台中使用 QEMU 模拟器运行 Linux 操作系统就是一种很常见的做法.

根据 RISC-V 社区的统计 [53] ,目前公开发布并已经提交到社区的 RISC-V 模拟器共有 24 种,服务于各类

RISC-V 研发项目之中.它们的各自特性见表 9.

这些模拟器中,Spike 和 QEMU 是 RISC-V 国际基金会推荐使用的:它们支持几乎所有的 RISC-V 指令集,

功能齐全,适用范围广,可模拟通用和嵌入式等多种处理器环境.基于这两种模拟器的研究成果也很丰富,如 Li

等人 [54] 在 QEMU 模拟器上进行了安全机制方面的研究,并定量分析了该成果对于 QEMU 模拟器的影响.此

外,Ripes 和 WebRISC-V 等模拟器的可视化程度较高,可以直观了解硬件平台的运行情况,入门较容易.Jupiter、