Page 339 - 《软件学报》2021年第12期

P. 339

刘畅 等:RISC-V 指令集架构研究综述 4003

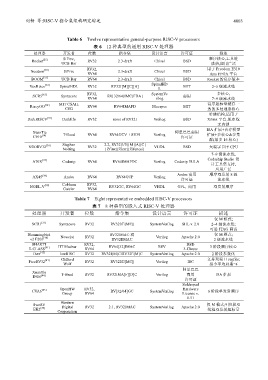

Table 6 Twelve representative general-purpose RISC-V processors

表 6 12 种典型的通用 RISC-V 处理器

处理器 开发者 位数 指令集 设计语言 许可证 描述

Rocket [25] SiFive, RV32 2.3-draft Chisel BSD 顺序核心,工具链

UCB Bar 成熟,应用广泛

freedom [30] SiFive RV32, 2.3-draft Chisel BSD 用于 Freedom E310

RV64 Arty FPGA 平台

BOOM [31] UCB Bar RV64 2.3-draft Chisel BSD Rocket 的乱序版本

VexRiscv [32] SpinalHDL RV32 RV32I[M][C][A] SpinalHD MIT 2~5 级流水线

L

SCR5 [33] Syntacore RV32, RV[32/64]IMC[FDA] SystemVe 商用 多核心,

RV64 rilog 7~9 级流水线

RiscyOO [34] MIT CSAIL RV64 RV64IMAFD Bluespec MIT 乱序超标量缓存一

CSG 致的多处理器核心

哈佛结构,适用于

DarkRISCV [35] Darklife RV32 most of RV32I Verilog BSD Xilinx 平台,流水线

无内锁

ISA 扩展+内存模型

XuanTie T-Head RV64 RV64GCV + SV39 Verilog 阿里巴巴商用

C910 [14] 许可证 扩展+多核心&多集

群(最多 16 核心)

NEORV32 [36] Stephan RV32 2.2, RV32[I/E][M][A][C] VHDL BSD 大端字节序 CPU

Nolting [Zfinx][Zicsr][Zifencei]

7~9 级流水线,

A70X [37] Codasip RV64 RV64IMAFDC Verilog Codasip EULA Codaship Studio 设

计工具集支持,

应用广泛

Andes 商用 顺序双发射 8 级

[38]

AX45 Andes RV64 RV64GCP Verilog

许可证 流水线

NOEL-V [39] Cobham RV32, RV32GC, RV64GC VHDL GPL, 商用 双发射顺序

Gaisler RV64

Table 7 Eight representative embedded RISC-V processors

表 7 8 种典型的嵌入式 RISC-V 处理器

处理器 开发者 位数 指令集 设计语言 许可证 描述

仅 M 模式;

SCR1 [21] Syntacore RV32 RV32I/E[MC] SystemVerilog SHL v. 2.0 2~4 级流水线;

可选 JTAG 调试

Hummingbird RV32IMAC 或 仅 M 模式;

v2 E203 [40] Newclai RV32 RV32EMAC Verilog Apache 2.0 2 级流水线

SHAKTI RV32, BSD

E-CLASS [41] IIT Madras RV64 RV64[32]IMAC BSV 3-Clause 3 阶段顺序核心

Ibex [42] lowRISC RV32 RV32I[M]C/RV32E[M]C SystemVerilog Apache 2.0 2 阶段参数化

PicoRV32 [43] Clifford RV32 RV32I/E[MC] Verilog ISC 支持双端口 regfile;

Wolf 指令平均周期=4

阿里巴巴

XuanTie

E906 [44] T-Head RV32 RV32IMA[F][D]C Verilog 商用 ISA 扩展

许可证

Solderpad

CVA6 [45] OpenHW RV32, RV[32/64]GC SystemVerilog Hardware 6 阶段单发射顺序

Group RV64 License v.

0.51

Western

SweRV 仅 M 模式;9 阶段双

EH2 [46] Digital RV32 2.1, RV32IMAC SystemVerilog Apache 2.0 线程双发射超标量

Corporation