Page 341 - 《软件学报》2021年第12期

P. 341

刘畅 等:RISC-V 指令集架构研究综述 4005

Vulcan、EmulsiV 等以教学为目的的模拟器,内容简化,对初学者相对友好,易于以此为基础开展进一步的研究.

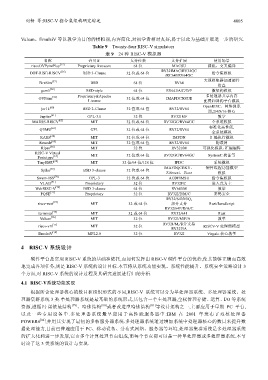

Table 9 Twenty-four RISC-V simulators

表 9 24 种 RISC-V 模拟器

名称 许可证 支持位数 支持扩展 使用场景

riscvOVPsimPlus [55] Proprietary freeware 64 位 MACSU 裸机、交叉编译

DBT-RISE-RISCV [56] BSD 3-Clause 32 位或 64 位 RV32IMAC/RV32GC 指令集模拟

/RC64I/RV64GC

FireSim [57] BSD 64 位 RV64 大规模集群加速硬件

仿真

gem5 [58] BSD-style 64 位 RV64I/A/C/D/F 微架构模拟

OVPsim [59] Proprietary&Apache 32 位或 64 位 IMAFDCNSUE 多处理器共享内存

License 配置和异构平台模拟

jor1k [60] BSD 2-Clause 32 位或 64 位 RV32/RV64 OpenRISC、网络浏览

器,2/4/8/16 核心

Jupiter [61] GPL-3.0 32 位 RV32IMF 教学

MARSS-RISCV [62] MIT 32 位或 64 位 RV32GC/RV64GC 全系统模拟

标准化高性能,

[63]

QEMU GPL 32 位或 64 位 RV32/RV64

全系统模拟

RARS [64] MIT 32 位或 64 位 IMFDN 汇编执行模拟

Renode [65] MIT 32 位或 64 位 RV32/RV64 物联网

Ripes [66] MIT 32 位 RV32I/M 可视化模拟、汇编编辑

RISC-V Virtual MIT RV32GC/RV64GC

Prototype [67] 32 位或 64 位 SystemC 验证等

TinyEMU [68] MIT 32 位/64 位/128 位 IFDC 系统模拟

IMAFDQCBKV、 硬件线程功能模型

Spike [69] BSD 3-clause 32 位或 64 位

Zifencei、Zicsr 模拟

Swerv-ISS [70] GPL-3 32 位或 64 位 ACDFIMSU 指令集模拟

VLAB [71] Proprietary 32 位 RV32EC 嵌入式为主

WebRISC-V [72] BSD 3-clause 64 位 RV64I/M 教学

PQSE [73] Proprietary 32 位 RV32I/E/M/C 密码安全

RV32/64I/M/Q,

riscv-rust [74] MIT 32 或 64 位 部分支持 Rust/JavaScript

RV32/64F/D/A/C

terminus [75] MIT 32 或 64 位 RV32/64I Rust

Vulcan [76] MIT 32 位 RV32I/M/F/A 教学

riscv-vm [77] MIT 32 位 RV32I/M,部分支持 RISCV-V 处理器模型

RV32F/A

EmulsiV [78] MPL2.0 32 位 RV32I Virgule 核心教学

4 RISC-V 系统设计

硬件平台是实现 RISC-V 系统的基础和依托,而如何发挥出 RISC-V 硬件平台的优势,使其能够正确而高效

地完成各项任务,则是 RISC-V 系统的设计目标.本节将从系统功能实现、系统性能提升、系统安全策略设计 3

个方面,对 RISC-V 系统的设计过程及其研究进展进行归纳分析.

4.1 RISC-V系统功能实现

根据所含处理器核心的数目和组织形式的不同,RISC-V 系统可以分为单处理器系统、多处理器系统、处

理器集群系统 3 类.单处理器系统是最基础的系统形式,只包含一个主处理器,全权管理存储、运算、I/O 等系统

资源,遵循冯·诺依曼结构 [79] 、哈佛结构 [80] 或者改进型哈佛结构 [81] 等设计架构之一,主要应用于早期 PC 平台,

以及一些专用设备中.多处理器系统最早应用于高性能服务器中:IBM 在 2001 年发布了双核处理器

POWER4 [82] ,并用其实现了最初的多核服务器系统.多处理器系统通过增加系统中处理器核心的数目来提升数

据处理能力,目前已普遍应用于 PC、移动设备、分布式网络、服务器等环境.处理器集群系统是多处理器系统

的扩大化和进一步发展,它由多个计算处理节点组成,而每个节点都可以是一种单处理器或多处理器系统.本节

讨论了这 3 类系统的设计与实现.