Page 84 - 《真空与低温》2025年第5期

P. 84

陈益峰等:深层放电脉冲特征模拟及对 MOS 器件损伤试验 623

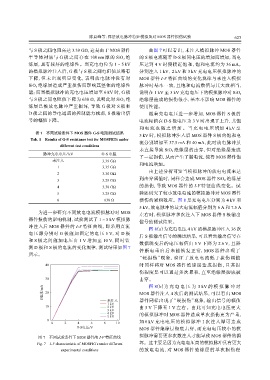

与 S 极之间电阻高达 3.39 GΩ,这是由于 MOS 器件 由图 7 可以看出,未注入模拟脉冲 MOS 器件

半导体衬底与 G 极之间存在 100 nm 厚的 SiO 2 绝 的 S 极电流随着 D-S 极间电压的增加而增加,当电

缘层,具有较好的绝缘性。当充电电位为 1~5 kV 压达到 4 V 时便接近饱和,饱和电流约为 36 mA。

的模拟脉冲注入后,G 极与 S 极之间电阻值虽略有 分别注入 1 kV、2 kV 和 3 kV 充电电压模拟脉冲的

下降,但未出现明显变化,表明放电脉冲没有对 MOS 器件 I-V 特征曲线的变化规律与未注入模拟

SiO 2 绝缘层造成严重损伤而影响其整体的绝缘性 脉冲时基本一致,且饱和电流数值与其大致相当,

能;而当模拟脉冲的充电电压增加至 6 kV 时,G 极 说明在 1 kV 至 3 kV 充电电压下的模拟脉冲对 SiO 2

与 S 极之间电阻值下降为 638 Ω,说明此时 SiO 2 绝 绝缘层造成的损伤很小,基本不影响 MOS 器件的

缘层已被放电脉冲严重损坏,导致 G 极对 S 极和 使用性能。

D 极之间的导电通道的控制能力减弱,S 极输出信 随着充电电压进一步增加,MOS 器件 S 极的

号的幅值下降。 电流幅值在 D-S 极电压为 3 V 时出现了上升,其饱

和 电 流 也 随 之 增 加 。 当 充 电 电 压 增加 4 kV 至

表 1 不同试验条件下 MOS 器件 G-S 电阻测试结果

5 kV 时,模拟脉冲注入后 MOS 器件 S 极的饱和电

Tab. 1 Results of G-S resistance test for MOSFETs under

流分别增加至 37.5 mA 和 40 mA,此时放电脉冲虽

different test conditions

未直接导致 SiO 2 绝缘层的击穿,但对绝缘层造成

脉冲充电电压/ kV G-S 电阻

了一定损伤,从而产生了漏电流,使得 MOS 器件饱

未注入 3.39 GΩ

和电流增加。

1 3.35 GΩ

由上述分析可知当模拟脉冲的放电电流未达

2 3.36 GΩ

到击穿阈值时,同样会造成 MOS 器件 SiO 2 绝缘层

3 3.29 GΩ

4 3.30 GΩ 的损伤,导致 MOS 器件的 I-V 特征曲线变化。试

5 3.25 GΩ 验还研究了较小放电电流的模拟脉冲对 MOS 器件

6 638 Ω 损伤的累积效应。图 8 是充电电压分别为 4 kV 和

5 kV,放电脉冲的最大电流幅值分别为 6 A 和 7.5 A

为进一步研究不同放电电流模拟脉冲对 MOS

左右时,模拟脉冲多次注入下 MOS 器件 S 极输出

器件损伤的影响机制,试验测试了 1~5 kV 模拟脉

信号的测试结果。

冲注入后 MOS 器件的 I-V 特征曲线,即采用直流

图 8(a)为充电电压 4 kV 的模拟脉冲注入 36 次

电压源分别对 G 极施加固定的电压 5 V,对 D 极

后 S 极输出信号的测试结果,可以看出输出信号在

和 S 极之间施加电压由 1 V 增加至 10 V,同时监

数据跳变后的电压幅值由 5 V 下降为 2.6 V,且器

测 D 极和 S 极的电流的变化规律,测试结果如图 7

件断电重启后未能恢复正常,MOS 器件出现了

所示。 “硬损伤”现象,验证了放电电流低于损伤阈值

40 时同样将对 MOS 器件绝缘层造成损伤,且其损

伤程度是可以通过多次累积,直至绝缘层彻底被

30 击穿。

8(b)为 充 电 电 压 为

的 模 拟 脉 冲 对

5 kV

S电流/mA 20 MOS 图 器件注入 4 次后的测试结果,可以看出 MOS

未注入 器件同样出现了“硬损伤”现象,输出信号的幅值

1 kV

10 2 kV 由 5 V 下降至 1 V 左右。由此可知充电电压更大

3 kV

4 kV 的模拟脉冲对 MOS 器件造成单次损伤更为严重,

5 kV

0 如 充电电压的模拟脉冲 1 次注入即可造成

0 2 4 6 8 10 6 kV

D-S电压/V MOS 器件绝缘层彻底击穿,而充电电压较小的模

拟脉冲需要更多次数注入才能导致 MOS 器件的损

图 7 不同试验条件下 MOS 器件的 I-V 特征曲线

坏。这主要是因为充电电压高的模拟脉冲具有更大

Fig. 7 I-V characteristic of MOSFETs under different

experimental conditions 的放电电流,对 MOS 器件绝缘层的单次损伤程