Page 75 - 《软件学报》2025年第10期

P. 75

4472 软件学报 2025 年第 36 卷第 10 期

完成采样运算之后, 需要在硬件层面对得到的多项式系数进行规整化操作, 进而满足多项式采样和多项式运

算的顶层流水线设计需求. 本文在上述两个采样模块的输出端分别设置了一个深度为 32、位宽为 184 的 FIFO 单

元用于多项式系数的缓存. 考虑到每两个 256 维的多项式系数是同步生成的, 因此设计了专用的、以单比特指示

信号 sel_fifo 为核心的功能控制逻辑, 旨在确定两个 FIFO 单元对应的读信号置高的时序位置, 从而确保采样得到

的多项式系数按照正确的顺序依次参与下一步的脉动阵列运算. 具体地, 当向量或矩阵中的多项式个数为偶数时,

FIFO 0 和 FIFO 1 的读信号分别依次置高, 且最后参与运算的多项式系数来自 FIFO 1 单元中的暂存数据, 如向量

s 2 所示. 当向量或矩阵中的多项式个数为奇数时, FIFO 单元的读信号时序逻辑不变, 但最后参与运算的多项式系

数来自 FIFO 0 单元, 且 FIFO 1 单元中的采样数据将被同步释放. 由于采样模块得到新的多形式系数最快需要 48

个时钟周期, 远大于 FIFO 单元中暂存数据的完整输出时间, 因此不会出现时序冲突和数据覆盖. 本文以更少的硬

件资源消耗实现了二并行的采样运算, 同时在顶层的硬件架构上保持了较高的时钟频率, 有效提高了整体的签名

运算效率.

3.5 可重构存储阵列设计

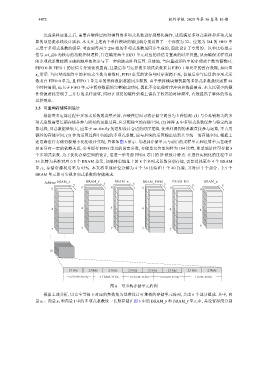

根据签名运算过程中多项式系数的类型差异, 在硬件层面可将存储空间分为 3 种情况: (1) 与公私钥相关的多

项式系数需要长期存储并参与所有的运算过程, 应分配独立的存储空间; (2) 矩阵 A 中多项式系数仅参与特定的运

算过程, 且总数据量较大, 应基于 on-the-fly 的思想设计合适的时序逻辑, 使采样得到的系数直接参与运算, 不占用

额外的存储空间; (3) 作为运算过程中间值的多项式系数, 应与后续的运算输出结果共享统一的存储空间. 根据上

述思路进行存储资源最小化的设计实现, 具体如图 6 所示. 考虑到存储单元与前后的采样单元和运算单元在硬件

层面具有一定的依赖关系, 参考缓存 FIFO 单元的设定参数, 存储单元位宽同样为 184 比特, 即单地址位可存储 8

个多项式系数. 为了优化存储空间的设计, 需进一步考虑 FPGA 芯片的 IP 核设计特点. 在进行实例化的过程中以

36 比特为基准对应 0.5 个 BRAM 单元, 如果将单地址上的 8 个多项式系数分别存储, 需要消耗至少 4 个 BRAM

单元, 存储资源利用率为 63%. 本文将单地址位分解为 4 个 36 比特和 1 个 40 比特, 共对应 5 个部分、2.5 个

BRAM 单元即可实现多项式系数的存储需求.

Address BRAM_s BRAM_t 5 BRAM_w 5 BRAM_PWM BRAM_RO BRAM_y

5 5 5 5

0 0 0 0 0 0

4 4 4 4 4 4

. . . . . . . . . . . . 6 .

7 . . 7 . 7 . 7 . . 7 . . .

. .

. .

. .

14

23bits 23bits 23bits 23bits 23bits 23bits 23bits 23bits

0.5 RAM: 36 bits 0.5 RAM: 36 bits 0.5 RAM: 36 bits 0.5 RAM: 36 bits 1 RAM: 40 bits

图 6 可重构存储单元阵列

根据上述分析, 以安全等级 5 对应的参数集为基准设计可重构的存储单元阵列, 共由 6 个部分组成. 其中, 向

t

量 s 1 、向量 s 2 和向量 中的多项式系数统一长期存储在图 6 中的 BRAM_s 和 BRAM_t 单元中, 其设置深度分别