Page 71 - 《软件学报》2025年第10期

P. 71

4468 软件学报 2025 年第 36 卷第 10 期

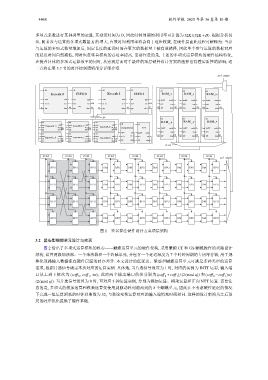

多项式系数进行某种类型的运算, 其延迟时间为 D, 因此时钟周期的利用率可计算为 32K/(32K +D). 根据分析易

知, 随着参与运算的多项式数量 K 的增大, 有效时间利用率将会向 1 逐步收敛, 在硬件层面此过程可解释为: 当参

与运算的多项式数量增加后, 固定长度的延迟时间在更大的数据量上被有效稀释, 因此单个参与运算的数据对应

的延迟时间自然减低, 同时也意味着模块的吞吐率提高. 需要注意的是, 上述的多项式运算模块的硬件结构特征,

在提升具体的多项式运算效率的同时, 从宏观层面对于最终的顶层硬件设计方案的选择也有着实质性的影响, 这

一点将在第 3.7 节的时序控制逻辑部分详细介绍.

sel_state

clk clk clk clk clk clk clk

Keccak0 FIFO0 Keccak 1 FIFO1 RAM_s RAM_t RAM_w

start end ept full start end ept full waddr raddr waddr raddr waddr raddr

en_in en_o wen ren req en_in en_o wen ren req wen ren wen ren wen ren

32 dout 64 req dout 64 32 dout 64 dout 64 184 din dout 184 184 din dout 184 184 din dout 184

din din din din

sel_fifo

clk clk clk

clk clk clk RAM_ y RAM_ p RAM_r

start end start ExpandMask_0 end start end clk clk

ExpandA_0 req ExpandS_0

req en_o 184 req en_o 160 en_o 32 SampleInBall RAM waddr raddr waddr raddr waddr raddr

din dout din dout din dout

start end waddr raddr wen ren wen ren wen ren

clk clk clk 184 184 184 184 184 184

start ExpandA_1 end start ExpandMask_1 end start ExpandS_1 end en_in en_o wen ren din dout din dout din dout

req en_o req en_o req en_o din dout din

din dout 184 din dout 160 din dout 32 dout

sel_state

ROM ROM ROM ROM ROM ROM ROM ROM

sel_state

BFU BFU BFU DM BFU DM BFU DM BFU DM BFU DM BFU

BFU BFU BFU DM BFU DM BFU DM BFU DM BFU DM BFU

BFU BFU BFU DM BFU DM BFU DM BFU DM BFU DM BFU

BFU BFU BFU DM BFU DM BFU DM BFU DM BFU DM BFU

图 1 签名算法硬件设计方案顶层架构

3.2 紧凑型蝴蝶单元设计与实现

图 2 给出了多项式运算模块的核心——蝴蝶运算单元的硬件架构, 采用兼顾 CT 和 GS 蝴蝶操作的双路设计

结构, 设置两级加法器、一个乘法器和一个约减单元, 并包含一个延迟深度为 7 个时钟周期的专用寄存器, 用于规

整化双路输入数据流在硬件层面的时序差异. 本文设计的低延迟、紧凑型蝴蝶运算单元可满足多种类型的运算

需求, 根据片选信号确定本次对应的运算实例. 具体地, 当片选信号设置为 1 时, 对应的实例为 INTT 运算, 输入端

口从上到下依次为 (coff , coff , tw), 此时两个输出端口的值分别为 (coff +coff )/(2(mod q)) 和 (coff −coff )w/

0

1

0

1

1

0

(2(mod q)). 当片选信号设置为 0 时, 可对应 3 种运算实例, 分别为模加运算、模乘运算和正向 NTT 运算. 需要注

意的是, 多项式的模加运算和模乘运算仅使用到脉动阵列前两列的 8 个蝴蝶单元, 因此在不考虑硬件延迟的情况

下完成一组运算消耗的时钟周期数为 32, 与数论变换运算对应的输入端填充时间相同. 这样的设计架构为之后顶

层的时序优化提供了硬件基础.