Page 74 - 《软件学报》2025年第10期

P. 74

胡跃 等: 基于 FPGA 的格基数字签名算法硬件优化 4471

为 184 比特的长寄存器, 可用于脉动阵列单元输入输出端的数据缓存. 同时, 将暂存的操作数按照寄存器的索引值

依次进行延迟对齐操作, 在经过固定数量的时钟周期之后, 可确保产生 8 个满足运算需求的系数组. 使用两组寄存

器依次交替进行上述操作, 最终可实现多项式运算及对应的重排序操作的流水线运行模式.

3.4 双核哈希模块设计

生成随机比特流是采样算法的前置运算, 其性能的差异将直接影响后续的采样模块的运行效率. 如上文所述,

在 Dilithium 算法中使用 SHAKE128 和 SHAKE256 两种计算实例生成随机比特流, 其中最核心的 3 个采样运算为

ExpandS、ExpandMask 和 ExpandA, 分别对应向量 s、向量 y 和矩阵 A 的多项式系数采样过程, 其余的计算过程

主要负责生成数据摘要或生成随机种子. 本文深入研究并总结了这两类运算的特点, 并得到如下结论: 采样算法

ExpandS、 ExpandA 和 ExpandMask 的输入参数长度均小于 XOF 计算实例输入数据的分组长度, 这意味着在进行

系数采样时, 哈希模块仅在开始阶段需要输入数据, 而在后续的迭代步骤中, 不存在将上一阶段运算结果与新输入

数据进行异或操作的运算过程, 这为哈希模块的优化提供了基础条件. 根据上述分析, 本文综合考虑了硬件资源和

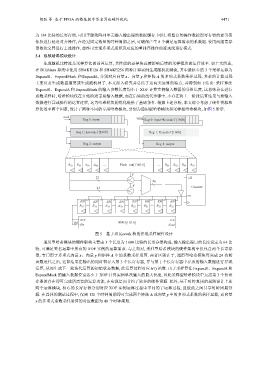

算法效率两个因素, 设计了两种不同的专用哈希模块, 分别为通用型哈希模块和采样型哈希模块, 如图 5 所示.

seed seed

Reg 0: input Reg 0: input+Keccak-f [1600]

Reg 1: Keccak-f [1600] Reg 1: Keccak-f [1600]

Reg 2: output Reg 1: output

... Hash_out[1343:0] ...

R 63 R 63 R 63 R 63 R 63 R 63 R 63 R 63

q

23 clk

46

q

23 Counter

en

EN EN EN EN EN EN EN EN

R 23 R 23 R 23 R 23 R 23 R 23 R 23 R 23

wen ren

183 FIFO[183:0]

din dout

图 5 基于双 Keccak 核的拒绝采样硬件设计

通用型哈希模块的硬件架构主要由 3 个长度为 1 600 比特的长寄存器构成, 输入输出端口的长度设定为 64 比

特, 可满足签名运算中所有的 XOF 实例的运算需求. 与之相对, 采样型哈希模块的硬件架构中仅包含两个长寄存

器, 专门用于多项式向量 s、向量 y 和矩阵 A 中的系数采样运算. 两者区别在于, 通用型哈希模块每完成 24 次轮

函数迭代之后, 运算结果在输出的同时暂存入第 3 个长寄存器, 并与第 1 个长寄存器中存放的输入数据进行异或

运算, 从而生成下一轮迭代运算的初始状态数据, 此运算过程对应 H() 函数. 由于采样算法 ExpandS、 ExpandA 和

ExpandMask 的输入数据位宽远小于 XOF 计算实例单次输入的最大长度, 因此采样型哈希模块中无需第 3 个长寄

存器的存在即可完成所需要的运算功能, 在实现层面节约了较多的硬件资源. 此外, 基于时钟复用的思路设计上述

两个运算模块, 核心的长寄存器分别对应 XOF 实例运算过程中不同的子运算过程, 且彼此之间共享时钟周期资

源. 在具体的测试过程中, 仅需 120 个时钟周期即可完成两个矩阵 A 或向量 y 中的多项式系数的采样运算, 而向量

s 的多项式系数采样运算的对应数据为 48 个时钟周期.