Page 77 - 《软件学报》2025年第10期

P. 77

4474 软件学报 2025 年第 36 卷第 10 期

(0,l×32), 可完整遍历 BRAM_y 单元的所有地址位, 读取数据

算需求. 具体地, 计数器 raddr RO 的工作范围设定为

并进行对应的重排序操作, 并基于表 1 给出的映射规则和时钟延迟生成 BRAM_RO 单元的写地址 waddr RO . 另一

ctr k 启动并完成一次 32 时钟周期的循环遍历, 用于生

方面, 矩阵 A 中的一个完整的多项式采样生成后, 主计数器

成 BRAM_RO 单元的读地址. 在此基础上, 辅计数器 ctr k_v2 在延迟 8 个时钟周期后开始启动, 并生成 32 个自然顺

序排列的写地址数据, 从而完成一次完整的点乘运算. 需要注意的是, 重排序操作持续运行并先于第 1 次点乘运算

启动时间至少 32 个时钟周期, 这样的设计可避免两个过程的时序冲突, 确保运算结果的正确性.

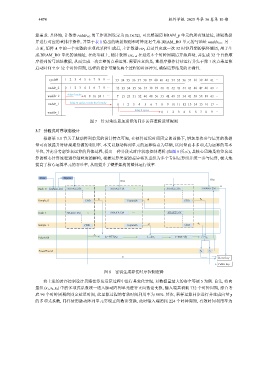

cycle# 1 2 3 4 5 6 7 8 9 ... 33 34 35 36 37 38 39 40 41 42 34 35 36 37 38 39 40 41 ...

raddr_2 0 1 2 3 4 5 6 7 8 ... 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 ...

delay 4 cycles ... ...

waddr_2 0 8 16 24 1 7 15 23 31 32 40 48 56 33 41 49 57 34 42 50 58 19 43

raddr_1 delay 32 cycles, reorder the first poly 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 ...

delay 8 cycles ...

waddr_1 0 1 2 3 4 5 6 7 8 9

图 7 针对乘法累加运算的同步访存逻辑运算规则

3.7 分段式时序状态设计

根据第 3.1 节关于脉动阵列单元的设计特点可知, 在硬件延迟时间固定的前提下, 增加单次参与运算的数据

量可有效提升时钟周期资源的利用率. 本文以脉动阵列单元的运算特点为基础, 以向量而非多项式为运算的基本

单位, 并充分考虑签名运算的具体过程, 提出一种分段式时序状态控制逻辑 (如图 8 所示), 其核心思路是将签名运

算的核心计算流程进行细粒度的解构, 根据运算类型的差异将其重组为多个专用运算组并统一参与运算, 极大地

提高了核心运算单元的吞吐率, 从而提升了硬件架构的整体运行效率.

Zeta Sigma

Rho Rho

tr

Hash_0 SHAKE 256 SHAKE 256 … SHAKE 128 … SHAKE 256 SHAKE 256

1 s s 2

Sample_0 CBD ExpandA A CBD

Hash_1 SHAKE 256 … SHAKE 128 … SHAKE 256

Sample_1 CBD ExpandA A CBD 2 s

1 s

=

PolyArith sˆ 1 = NTT(s 1 ) ˆ t = ˆ 1 s · A ˆ t=NTT −1 (t) ˆ t+ s 2

PowerRound t 0 t 1

K Secret key

Public key

图 8 密钥生成算法时序控制逻辑

将上述的时序控制设计思路在签名运算过程中进行具象化实现, 以数据量最大的安全等级 5 为例. 首先, 将向

量组 (s 1 , s 2 , t 0 ) 中的多项式系数统一送入脉动阵列单元进行正向数论变换, 输入端共消耗 732 个时钟周期, 综合考

虑 96 个时钟周期的固定延迟时间, 此运算过程的有效时间利用率为 88%. 其次, 采样运算同步进行并生成向量 y

的多项式系数, 同样使用脉动阵列单元实现正向数论变换, 此时输入端消耗 224 个时钟周期, 有效时间利用率为