Page 464 - 《软件学报》2025年第5期

P. 464

2364 软件学报 2025 年第 36 卷第 5 期

2) 基于内核的寄存器组设计, 提出了 BankedIPC, 实现快速上下文切换的同时, 使用空闲寄存器传递 IPC 数

据, 将寄存器 IPC 的思想应用在 SPARC 架构上;

3) 针对 SPARC 多核处理器, 提出了 FlexIPC 以优化跨核 IPC 的性能;

4) 在航天领域使用的真实硬件 S698PM 上对 ChCore 上优化前后的 IPC 性能进行了测试, 测试表明优化后

IPC 时延降低至 50%.

1 背景知识

1.1 SPARC 架构及其寄存器窗口机制

SPARC 架构在提出时是一种灵活度较高且具有可扩展性的设计并取得了较大成功. 一方面, Sun Microsystem

公司在其工作站和服务器环境上广泛采用了 SPARC 架构的处理器; 另一方面, 欧洲航天局也基于 SPARC 架构开

发 ERC32 处理器 [11] , 用于嵌入式航空航天设备中. 进入 21 世纪后, LEON 系列的 SPARC 架构处理器在欧洲航天

设备及国际空间站上被广泛应用, 成为航天领域内的主流处理器. 中国在发展航天事业的过程中, 也在航天设备上

采用了 SPARC 架构的处理器 [39] , 并自主研发了 BM3803, BM3823, BM3883 系列 [14] 以及 S698 系列 [15] SPARC 架

构处理器, 目前也逐步应用到了航天设备上.

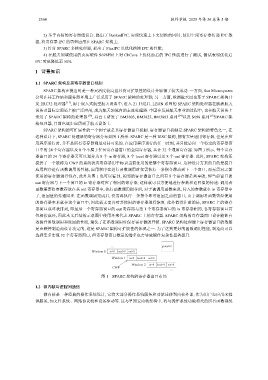

SPARC 架构的可扩展性的一个例子就是其寄存器窗口机制. 寄存器窗口机制是 SPARC 架构的特色之一, 在

这种设计下, SPARC 处理器的寄存器分布如图 1 所示. SPARC 是一种 RISC 架构, 拥有大量通用寄存器, 但是在应

用程序运行时, 并不是所有寄存器都是对其可见的. 在应用程序运行的任一时刻, 其只能访问一个特定的寄存器窗

口中的 24 个寄存器以及 8 个不属于任何寄存器窗口的全局寄存器, 共计 32 个通用寄存器. 如图 1 所示, 每个寄存

器窗口的 24 个寄存器又可以划分为 8 个 in 寄存器, 8 个 local 寄存器以及 8 个 out 寄存器. 此外, SPARC 架构还

提供了一个被称为 CWP 的系统状态寄存器用于标识当前使用的是哪个寄存器窗口. 这种设计方案的目的是提升

应用程序进行函数调用的性能, 应用程序在进行函数调用时仅需执行一条指令滑动到下一个窗口, 而无需对之前

使用的寄存器进行保存, 此外从图 1 也可以看到, 相邻的寄存器窗口之间有 8 个寄存器是共享的, 即当前窗口的

out 寄存器与下一个窗口的 in 寄存器对应了相同的寄存器, 这样就可以方便地进行参数和返回值的传递: 调用者

函数需要将参数存放在其 out 寄存器中, 执行函数调用指令后, 对于被调用函数来说, 传入的参数就在 in 寄存器中

了, 返回值的传递同理. 在函数调用完成后, 仅需再执行一条指令即可返回之前的窗口, 由于调用者函数曾经使用

的寄存器本来就在这个窗口中, 因此就无需再对其使用的寄存器进行恢复. 此外值得注意的是, SPARC 上的寄存

器窗口成环状排列, 即最后一个寄存器窗口的 out 寄存器与第 1 个寄存器窗口的 in 寄存器相同, 各寄存器窗口首

位相接成环, 因此本文后续的示意图中使用环来代表 SPARC 上的寄存器. SPARC 架构的寄存器窗口设计能够有

效提升函数调用和返回的性能, 避免了在函数调用时保存寄存器的开销. SPARC 架构处理器上寄存器窗口的数量

是由硬件制造商设计决定的, 这是 SPARC 架构可扩展性的体现之一. 为了达到更好的函数调用性能, 制造商可以

选择至多实现 32 个寄存器窗口, 但寄存器窗口数量的增多也会导致硬件复杂性显著提升.

… global×8

Window 0 in×8 local×8 out×8

Window 1 in×8 local×8 out×8

Window 2 in×8 local×8 out×8

CWP

…

图 1 SPARC 架构的寄存器窗口布局

1.2 微内核与进程间通信

微内核是一种经典的操作系统设计, 它将大部分操作系统服务和功能迁移到内核外部, 作为用户态应用来提

供服务, 如文件系统、网络协议栈和设备驱动等. 这与早期宏内核架构中, 将与操作系统功能相关的所有函数都统