Page 121 - 《软件学报》2020年第10期

P. 121

刘焰强 等:FPGA 加速系统开发工具设计:综述与实践 3097

通过统计软件应用过滤 512MB 随机数据的平均(1 000 次)任务运行时间,可以得到表 4 展示的随单次传输

块大小的增加而变化的加速比,受限于实验使用的 FPGA 资源总量和我们采用的过滤器设计,单次传输 32KB 是

我们能在 250MHz 下运行的最优值.从实验结果来看,VeriScala 框架能够有效地构建 CPU+FPGA 的加速系统.

Table 4 Performance comparison between FPGA accelerated filter and CPU filter

表 4 FPGA 加速过滤器和 CPU 过滤器的性能对比

块规模(KB) 4 8 16 32

CPU (ms) 1 559 1 559 1 559 1 559

FPGA (ms) 1 675 1 198 996 902

加速比 0.93X 1.30X 1.56X 1.73X

3 总结和展望

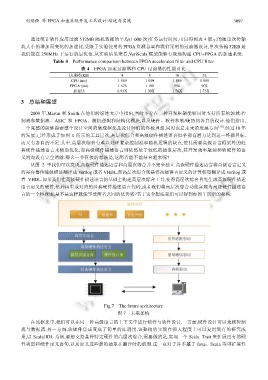

2009 年,Martin 和 Smith 在他们的综述文章中指出,当时不存在一种开发框架能够同时支持所有的领域:控

制流和数据流、ASIC 和 FPGA、随机逻辑和结构化模块,以及硬件、软件和软/硬协同各自的设计.他们指出,

一个完整的能够探索整个设计空间的集成框架是设计师们的终极理想,同时也是未来的发展方向 [18] .经过 10 年

的发展,已经形成了如图 1 所示的工具层次,高层次综合和高级硬件描述语言似乎都有潜力达到这一终极目标,

而又有各自的不足.其中,高层次综合有难以处理复杂控制流和随机逻辑的缺点,使其需要高级语言框架外的经

典硬件描述语言来辅助优化;而高级硬件描述语言则依然处于较低的抽象层次,其开发效率瓶颈和软硬件的语

义鸿沟没有完全消除.那么一个直接的想法是,这两者能不能结合起来呢?

从图 2 中我们可以发现,高级硬件描述语言和高层次综合并不完全独立.高级硬件描述语言将高级语言定义

的寄存器传输级描述翻译成 Verilog 或者 VHDL,而高层次综合则是将高级语言定义的计算模型翻译成 Verilog 或

者 VHDL.如果我们在高级硬件描述语言的基础上构建高层次综合工具,使得高层次综合首先生成高级硬件描述

语言定义的硬件,然后再生成对应的经典硬件描述语言代码,或者我们将高层次综合功能实现为高级硬件描述语

言的一个特殊库,是不是这样就能享受两者共同的优势呢?基于这个想法我们可以得到如图 7 所示的架构.

Fig.7 The future architecture

图 7 未来架构

在该框架中,我们可以在同一种高级语言的上下文中进行硬件与软件设计,一方面,硬件设计可以兼顾控制

流与数据流,另一方面,软硬件集成变成了简单的库调用.该架构的实现在很大程度上可以复用现有的研究成

果,以 ScalaHDL 为例,要想支持某种特定硬件的高层次综合,需要做的是,实现一个 Scala Trait 来扩展已有的硬

件类型和硬件定义语句,以及定义这些新的抽象在翻译时的机制.这一点对于许多基于 Java、Scala 等可扩展性