Page 117 - 《软件学报》2020年第10期

P. 117

刘焰强 等:FPGA 加速系统开发工具设计:综述与实践 3093

个问题.本节将介绍我们实现的 ScalaHDL 硬件描述语言,以及基于 ScalaHDL 的开发框架 VeriScala.

2.1 设计目标

基于高级硬件描述语言的加速系统开发框架设计目标主要有两方面:充分利用高级语言在开发效率、维护

管理上的优势并提供简便的集成策略.具体来说有以下几点.

(1) 支持丰富的代码重用机制.需要提供包括继承、参数化类型在内的特性来提高代码重用率和可维

护性.

(2) 易用的语言抽象.一方面需要通过支持面向对象编程来进行模块化设计,另一方面还需要将 RTL 抽象

在高级语言中进行映射以帮助软件工程师的理解.

(3) 支持库的设计和使用.需要通过支持硬件设计的引用方法,让现有设计逐渐形成丰富的生态,进一步

提高生产效率.

(4) 支持软件模拟.需要设计对接的软件模拟器,让高级语言定义的硬件设计直接利用高级语言的测试框

架进行测试.

(5) 支持快速的系统集成和部署.需要在框架内处理好底层硬件数据传输机制,并提供简洁的软件接口.

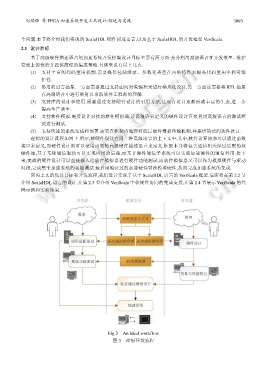

理想的设计流程如图 3 所示,软硬件设计在同一种高级语言的上下文中,其中,软件计算需求可以通过函数

接口来定义,而硬件设计则可以使用内嵌的高级硬件描述语言来定义.框架本身将包含通信相关经过适配的软

硬件库,基于基础通信驱动可以实现应用的后端,而基于硬件通信子系统可以实现加速硬件的通信外围.接下

来,完成的硬件设计可以直接输入给软件模拟器进行硬件功能测试,而软件模拟器又可以作为模拟硬件与驱动

对接,完成整个加速系统的功能测试.最后用验证过的加速硬件替换模拟硬件,从而完成加速系统的集成.

面向上文的设计目标和开发流程,我们设计实现了基于 ScalaHDL 语言的 VeriScala 框架.后面将在第 2.2 节

介绍 ScalaHDL 语言的设计,在第 2.3 节介绍 VeriScala 中软硬件协同的集成支持,在第 2.4 节展示 VeriScala 的代

码示例和实验结果.

Fig.3 An ideal workflow

图 3 理想开发流程