Page 116 - 《软件学报》2020年第10期

P. 116

3092 Journal of Software 软件学报 Vol.31, No.10, October 2020

硬件描述语言大多成为了学术语言,较少在实际生产中得到应用.

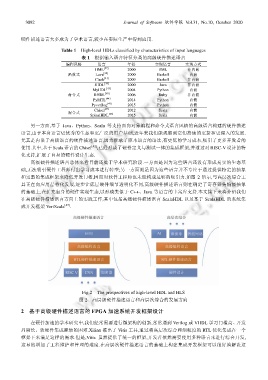

Table 1 High-level HDLs classified by characteristics of input languages

表 1 根据输入语言特征分类的高级硬件描述语言

编程风格 语言 年份 实现语言 实现方式

HML [37] 2000 SML 非内嵌

函数式 Lava [38] 2000 Haskell 内嵌

Clash [41] 2009 Haskell 非内嵌

JHDL [39] 2000 Java 非内嵌

MyHDL [43] 2004 Python 内嵌

命令式 RHDL [40] 2006 Ruby 非内嵌

PyMTL [44] 2014 Python 内嵌

Pyverilog [45] 2015 Python 内嵌

Chisel [42] 2012 Scala 内嵌

混合式 [46]

SpinalHDL 2015 Scala 内嵌

另一方面,基于 Java、Python、Scala 等支持面向对象编程和命令式语言风格的高级语言构建的硬件描述

语言,由于本身语言更优秀的生态和更广泛的用户基础,近年来我们能观察到它们持续的更新和更深入的发展.

尤其是内嵌于高级语言的硬件描述语言,因为继承了原本语言的语法,有更低的学习成本,吸引了更多开发者的

使用.其中,基于 Scala 语言的 Chisel [42] ,已经形成了硬件定义与测试一体的集成框架,并通过对 RISC-V 设计的特

化支持,扩展了自身的硬件设计生态.

高级硬件描述语言总体来看目前还处于学术研究阶段.一方面是因为这些语言还没有形成充实的生态基

础,无法吸引硬件工程师付出学习成本进行转型;另一方面则是因为这些语言并不专注于通过提供特定的抽象

和完整的集成框架来降低开发门槛,因而对软件工程师也未能构成足够的吸引力.如图 2 所示,与高层次综合工

具正在向应用层特化发展,逐步让底层硬件细节透明化不同,高级硬件描述语言则在确定了寄存器传输级抽象

的基础上,在扩充自身的硬件实现生态,以形成类似于 C++、Java 等语言的丰富库支持.本文接下来将介绍我们

在高级硬件描述语言方向上的实践工作,其中包括高级硬件描述语言 ScalaHDL 以及基于 ScalaHDL 的系统集

成开发框架 VeriScala [47] .

Fig.2 The prospectives of high-level HDL and HLS

图 2 高层级硬件描述语言和高层次综合的发展方向

2 基于高级硬件描述语言的 FPGA 加速系统开发框架设计

在硬件加速的学术研究中,我们经常需要进行微架构的创新,常常遇到 Verilog 或 VHDL 学习门槛高、开发

周期长、软硬件集成麻烦的困难.Xilinx 推出了 Vitis 工具,通过将高层次综合和细粒度的 RTL 优化集成在一个

框架下来满足这样的需求.但是,Vitis 虽然提供了统一的框架,开发者依然需要使用多种语言来进行综合开发,

这显然增加了工程维护和管理的难度.在高层次硬件描述语言的基础上构建集成开发框架可以很好地解决这