Page 98 - 《真空与低温》2026年第1期

P. 98

刘 攀等:用于原子干涉的光学锁相环技术研究进展 95

路控制特性及智能化调控能力,光路集成方案则极 致压缩了 OPLL 尺寸,适用于高动态场景。

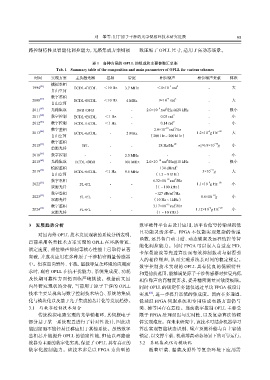

表 1 各种方案的 OPLL 的组成和主要参数汇总表

Tab. 1 Summary table of the composition and main parameters of OPLL for various schemes

时间 实现方案 主从激光器 拍频 带宽 相位噪声 相位噪声贡献 体积

模拟鉴相

−3

1994 [23] ECDL+ECDL <10 Hz 3.7 MHz <4×10 rad 2 - 大

自由空间

数字鉴相

−3

2008 [25] ECDL+ECDL <10 Hz 4 MHz 9×10 rad 2 - 大

自由空间

2

−9

2011 [67] 光路集成 DFB+DFB - - 2.0×10 rad /Hz @20 kHz - 极小

2011 [60] 数字控制 ECDL+ECDL <1 Hz - 0.03 rad 2 - 小

2012 [61] 数字控制 ECDL+ECDL <1 Hz - 0.14 rad 2 - 小

2

数字鉴相 2.0×10 rad /Hz

−10

−9

2013 [46] ECDL+ECDL - 2 MHz 1.2×10 g Hz −1/2 大

自由空间 (200 Hz~200 kHz)

数字鉴相

−10

2015 [33] EFL - - 28 Hz/Hz 1/2 σ a =6.9×10 g 小

单源光纤

2018 [63] 数字控制 - - 2.5 MHz - - 小

2

−10

2018 [69] 光路集成 ECDL+DBR - 100 MHz 2.0×10 rad /Hz@10 kHz - 极小

模拟鉴相 −130 dBrad 2

−11

2019 [38] ECDL+ECDL <1 Hz 9.5 MHz 3×10 g 大

自由空间 (1.5~9 kHz)

2

−12

数字鉴相 6.32×10 rad /Hz

[53] −9 −1/2

2022 FL+FL - - 1.1×10 g Hz 小

双源光纤 (1~100 kHz)

2

数字鉴相 −127 dBrad /Hz

−10

2023 [55] FL+FL - - 8.6×10 g 小

双源光纤 (10 Hz~1kHz)

数字鉴相 3.17×10 rad /Hz

−12

2

[34] −8 −1/2

2024 FL+FL - - 1.12×10 g Hz 小

双源光纤 (1~10 kHz)

3 发展趋势分析 数字硬件平台去设计应用,该平台信号传输延迟低

且功能灵活多样。FPGA 不仅能实现复杂的传递

对国内外 OPLL 技术发展现状的系统分析表明,

函数,还具备自动寻谱、动态锁频及远程监控等智

目前采用各类技术方案实现的 OPLL 在环路带宽、

能化调控能力。同时 FPGA 可以嵌入自适应 PID、

锁定速度、相位噪声抑制等核心性能上已取得显著

卡尔曼滤波等先进算法而有效抑制振动与温漂引

突破,并成功应用在多种原子干涉精密测量传感器

入的相位噪声,从而实现系统长时间的稳定锁定。

中。但在面向野外、车载、星载等复杂环境的应用需

数字控制技术实现的 OPLL 具有优良的低频特性

求时,现有 OPLL 在抗干扰能力、系统集成度、功耗 和宽捕获范围,能够满足原子干涉传感器对拉曼光低

及长期可靠性方面仍面临严峻挑战。根据前文国 相位噪声的高精度要求,提升精密测量灵敏度极限。

内外研究现状的分析,当前用于原子干涉的 OPLL 同时 OPLL 的锁定任务能仅通过单块 FPGA 板设计

技术主要呈现出与数字控制技术结合、系统的集成 实现 ,进一步提升系统的集成度。国内在多通道、

[66]

化与模块化以及基于光子集成的芯片化等发展趋势。 低延迟 FPGA 伺服系统和专用集成电路方面仍与

3.1 与数字控制技术结合 美、德等国存在差距。当前数字控制 OPLL 主要受

传统模拟电路实现的光学锁相环,其伺服电子 限于 FPGA 处理延迟与实时性,以及复杂算法的硬

部分基于某一系统配置进行了针对性设计,因此功 件实现难度。在未来研究中,该技术可结合机器学习

能固定而不能轻易迁移应用于其他系统。虽然数字 算法实现智能状态识别、噪声预测补偿与自主容错

鉴相芯片能提升 OPLL 的锁定性能,但是以环路滤 锁定,以支撑车载、机载等高动态场景下的可靠运行。

波器为主要的数字化实现,保证了 OPLL 具有真正的 3.2 系统集成化与模块化

数字化控制能力。该技术多是以 FPGA 为典型的 随着星载、船载及野外等复杂环境下应用需