Page 51 - 《软件学报》2025年第9期

P. 51

3962 软件学报 2025 年第 36 卷第 9 期

Spike 原有的缓存模型使用了简单的软件指令缓存来提升仿真速度. 当访问指令缓存时, 如果命中, 直接通过软件

指令缓存进行访问; 如果未命中, 则通过重新填充软件指令缓存进行访问. 为了不降低仿真速度, Spike-FlexiCAS

保留了软件指令缓存结构. 同时, 无论软件指令缓存是否命中, 地址转换完成后, 都会将指令读取请求同步到

FlexiCAS 的读接口. 清理/失效缓存块行为用于支持 RISC-V 指令集中 cbo_clean、cbo_flush 和 cbo_inval 等缓存

一致性维护指令. 执行清理/失效缓存块时, 将清理/失效请求同步至对应的 FlexiCAS 写回/冲刷接口.

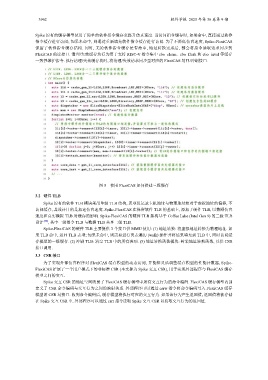

图 5 使用 FlexiCAS 如何搭建三级缓存

3.2 硬件 TLB

Spike 原有的软件 TLB 模块采用单级 TLB 结构, 表项仅记录主机地址与物理地址相对于虚拟地址的偏移, 不

访问缓存, 其设计目的是加速仿真速度. Spike-FlexiCAS 在保留软件 TLB 的基础上, 添加了硬件 TLB, 以兼顾仿真

速度和真实模拟 TLB 对缓存的影响. Spike-FlexiCAS 的硬件 TLB 架构基于 Coffee Lake (Intel Gen 9) 的二级 TLB

设计 [34] , 其中一级指令 TLB 与数据 TLB 共享二级 TLB.

Spike-FlexiCAS 的硬件 TLB 主要提供 3 个接口供 MMU 使用: (1) 地址转换: 将虚拟地址转换为物理地址. 如

果 TLB 命中, 返回 TLB 表项; 如果未命中, 则需要进行页表遍历 (walk) 操作并将结果填充到 TLB 中, 同时访问缓

存模型的一级缓存. (2) 冲刷 TLB: 清空 TLB 中的所有表项. (3) 地址转换函数模块: 封装地址转换函数, 以供 CSR

接口调用.

3.3 CSR 接口

为了实现外部仿真程序对 FlexiCAS 缓存模型的动态访问, 并能够灵活调整缓存模型的性能计数器, Spike-

FlexiCAS 扩展了一个用户模式下的非标准 CSR (本文称为 Spike 交互 CSR), 用于实现外部程序与 FlexiCAS 缓存

模型之间的交互.

Spike 交互 CSR 的地址空间映射了 FlexiCAS 缓存模型中所有交互行为的命令编码. FlexiCAS 缓存模型内部

定义了 CSR 命令编码与交互行为之间的映射关系. 外部程序可以通过 csrw 指令将命令编码写入 FlexiCAS 缓存

模型的 CSR 写接口. 收到命令编码后, 缓存模型将执行对应的交互行为. 如果该行为产生返回值, 返回值将被存储

在 Spike 交互 CSR 中. 外部程序可以通过 csrr 指令读取 Spike 交互 CSR 以获取交互行为的返回值.