Page 46 - 《软件学报》2025年第9期

P. 46

韩金池 等: Spike-FlexiCAS: 支持缓存架构灵活配置的 RISC-V 处理器模拟器 3957

的行为 (如运行指令数、内存访问地址等) 进行统计和分析, 因此 Pin 被广泛用于对程序的性能评估以及优化. ZSim [19]

和 Sniper [23] 都是执行驱动型的时序级体系结构模拟器, 它们在程序运行的过程中通过 Pin 获取指令流等信息, 并

以此来驱动整个模拟器的运行. 受 Pin 的限制, ZSim 只能作为 x86 指令集的模拟器, 而 Sniper 在最近的更新改动

中还添加了对 RISC-V 的支持 [24] , 但需要先由 Spike 跑完程序得到仿存序列, 再由 Sniper 的缓存模型进行重放.

Pycachesim [25] 和 Dinero IV [26] 都是轨迹驱动型的模拟器, 它们只包含内存子系统, 因此不能直接模拟程序的运

行, 只能以仿存序列作为输入模拟缓存的行为. Pycachesim 支持多级缓存, 上下级缓存间只支持包含性的包含关

系, 但它不支持多核缓存. Dinero IV 同样只支持包含性的包含关系, 它在支持多级缓存的同时还支持多核缓存,

Dinero IV 的出现更多是出于教学的目的. CacheFX [27] 是一个用于评估缓存安全性的框架, 它实现了 Ceaser [12] 、

Ceaser-S [13] 、ScatterCache [28] 等缓存架构. 由于 CacheFX 的产生是为了评估缓存的安全性, 因此它的仿真模式不同

于之前提到的任何一种模拟器. 它会模拟攻击者和受害者使用同一缓存的场景, 并假设一个受害者正在进行一些

敏感操作 (如 AES 加密等), 以此测试攻击者是否能在某一缓存架构下构建缓存驱逐集或获取受害者的一些信息.

但 CacheFX 的缓存结构只支持一级缓存, 它也无法对程序进行仿真. 因此使用者无法使用 CacheFX 运行测试集评

估缓存的性能.

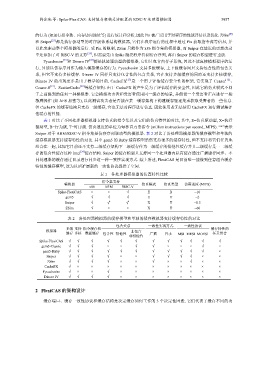

表 1 对比了不同处理器模拟器支持仿真的指令集以及它们的仿真特性的对比, 其中, E=仿真驱动型, X=执行

驱动型, B=行为级, T=时序级. 仿真速度的单位为每秒百万条指令 (million instructions per second, MIPS). “*”表示

Sniper 对于 ARM/RISC-V 指令集是仿存序列驱动型的模拟器. 表 2 对比了各处理器模拟器的缓存模型和单独的

缓存模拟器支持缓存特性的对比. 其中 gem5 的 Ruby 缓存模型虽然支持很多的缓存特性, 但不支持将它们任意地

组合在一起, 比如它目前还不支持三级缓存架构下二级缓存作为一级缓存的排他性缓存并且三级缓存是一二级缓

存的包含性缓存这种 Intel [29] 缓存结构. Sniper 的缓存模型只支持同一个处理器内私有缓存通过广播进行同步、不

同处理器的缓存通过目录进行同步这一种一致性实现方式. 综上所述, FlexiCAS 是目前唯一能做到任意组合缓存

特性的缓存模型, 这为以后扩展新的一致性协议提供了空间.

表 1 各处理器模拟器的仿真特性比较

指令集支持

模拟器 仿真模式 仿真类型 仿真速度 (MIPS)

x86 ARM RISC-V

Spike-FlexiCAS × × √ E B ~10

gem5 √ √ √ E T ~2

Sniper √ √ * √ * X T ~0.5

ZSim √ × × X T ~60

表 2 各处理器模拟器的缓存模型和单独的缓存模拟器支持缓存特性的对比

包含关系 一致性实现方式 一致性协议

多级 支持 指令缓存和 缓存特性的

模拟器 非包含

缓存 多核 数据缓存 包含性 排他性 广播 目录 MSI MESI MOESI 任意组合

非排他性

Spike-FlexiCAS √ √ √ √ √ √ √ √ √ √ √ √

gem5-Classic √ √ √ × × √ √ × × × √ ×

gem5-Ruby √ √ √ √ √ √ √ √ √ √ √ ×

Sniper √ √ √ √ × × √ √ √ √ × ×

ZSim √ √ √ √ × × √ × × √ × ×

CacheFX √ × × × × × × × × × × ×

Pycachesim √ × × √ × × × × × × × ×

Dinero IV √ √ √ √ × × × × × × × ×

2 FlexiCAS 的架构设计

缓存端口、缓存一致性协议和缓存结构是决定缓存如何工作的 3 个决定性因素, 它们代表了缓存不同的功