Page 49 - 《软件学报》2025年第9期

P. 49

3960 软件学报 2025 年第 36 卷第 9 期

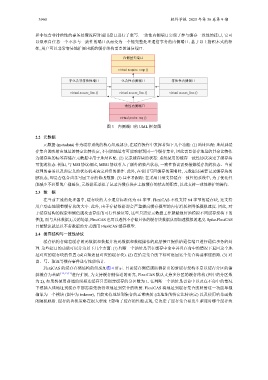

和非包含非排他性的事务处理流程对通用接口进行了重写. 一致性内侧端口实现了参与缓存一致性的接口, 它可

以继承自任意一个不参与一致性的端口从而变为一个能完整处理通信事务的内侧端口. 基于以上搭积木式的框

架, 用户可以非常容易地扩展出新的缓存结构需要的通信端口.

内侧基类端口

virtual acquire_resp ()

非包含非排他性端口 包含性内侧端口 排他性内侧端口

virtual access_line () virtual access_line () virtual access_line ()

一致性内侧端口

virtual probe_req ()

图 3 内侧端口的 UML 框架图

2.2 元数据

元数据 (metadata) 作为缓存系统的核心组成部分, 在缓存操作中发挥着如下几个功能: (1) 地址匹配: 地址到缓

存集合的映射由地址的特定比特决定, 不同的地址有可能映射到同一个缓存集合, 因此需要保存地址的其余比特作

为缓存块的标签存储在元数据中用于地址匹配. (2) 记录缓存块的状态: 系统使用的缓存一致性协议决定了缓存块

可能的状态. 例如, 与 MSI 协议相比, MESI 协议引入了额外的独占状态, 一致性协议需要根据缓存块的状态、当前

处理的事务以及预定义的状态机来决定后续的操作. 此外, 在使用写回缓存的策略时, 元数据还需要记录缓存块的

脏状态, 即是否包含尚未写回主存的修改数据. (3) 共享者跟踪: 在采用目录支持缓存一致性的系统中, 为了优化性

能减少不必要的广播通信, 元数据还承担了记录各缓存块在上级缓存的状态的职责, 以此支持一致性维护的操作.

2.3 数 据

在当前主流的处理器中, 缓存块的大小通常标准化为 64 字节. FlexiCAS 不仅支持 64 字节的缓存块, 还支持

用户动态地调整缓存块的大小. 此外, 由于存储数据却会严重提高缓存模型的内存消耗和降低模拟速度. 因此, 对

于缓存结构的探索和侧信道攻击算法的可行性验证等, 这些只需要元数据工作就能很好地模拟不同缓存架构下的

性能, 而与具体数据无关的场景, FlexiCAS 也可以选择不存储具体的缓存块数据从而加速模拟的速度. Spike-FlexiCAS

目前默认就是以不带数据的方式调用 FlexiCAS 缓存模型.

2.4 缓存结构与一致性协议

缓存结构存储着缓存的元数据和数据并将元数据和数据操作的底层接口提供给通信端口进行通信事务的处

理. 这些接口的功能可以分为以下几个方面: (1) 判断一个地址是否在缓存中命中并且在命中的情况下返回这个地

址对应的缓存块的位置 (或直接返回对应的缓存块). (2) 在给定集合的下标时返回这个集合将要驱逐的路. (3) 对

读、写、驱逐等缓存事件进行性能统计.

FlexiCAS 的缓存存储结构的组成如图 4 所示. 目前缓存侧信道防御提出的新缓存架构多是以缓存分区的偏

斜缓存为基础 [12,13,17] 进行扩展, 为支持缓存侧信道的研究, FlexiCAS 默认支持多分区的缓存结构 (图中的分区数

为 2), 如果想使用普通的组相连缓存只需指定缓存的分区数为 1. 在判断一个地址是否命中以及在不命中的情况

下想插入该地址到缓存中都需要先获得该地址到集合的映射. FlexiCAS 将地址到缓存集合的映射这一功能单独

抽象为一个模块 (图中为 indexer), 目前支持地址到集合的正常映射 (由地址的特定比特决定) 以及使用哈希函数

的随机映射. 缓存的替换策略在很大程度上影响了缓存的性能表现, 它决定了缓存集合要发生驱逐时哪个缓存块