Page 368 - 《软件学报》2025年第4期

P. 368

1774 软件学报 2025 年第 36 卷第 4 期

2

Tianjic [178] 是清华大学类脑计算研究中心设计的异构融合神经形态计算芯片, 尺寸为 14.44 mm , 采用 28 nm

工艺, 由 150 多个计算核心组成, 可满足约 4 万个神经元和 1 千万个突触的计算. TianJic 芯片的最大特点是将计

算科学和神经科学两个不同的人工智能研究方向进行了整合, 既能支持现有的机器学习算法, 也能支持神经形态

计算范式, 很好地融合了 ANN 与 SNN 各自的优势.

Darwin [179] 是浙江大学研究的全数字神经形态芯片, 采用 55 nm 工艺, 包含 576 个计算内核, 每个内核可实现

约 256 个神经元和 1 000 万个突触的计算. Darwin 芯片具有高度的可配置性, 支持神经元、突触及突触延迟的自

主配置, 适用于手势识别、图像识别、语音识别、脑电识别等多种应用.

全数字实现的电路具有很强的可编程性与灵活性, 支持 SNN 模型各种参数的配置, 大大缩短了开发时间, 而

且不受电源、热噪声或器件不匹配的影响. 在片上通信方面, 数电实现也能提供相当的稳定性和可靠性. 然而, 全

数字实现的电路会带来更多的硅片面积占用以及单位功能功耗.

3.2.3 神经形态芯片的现状总结与发展趋势

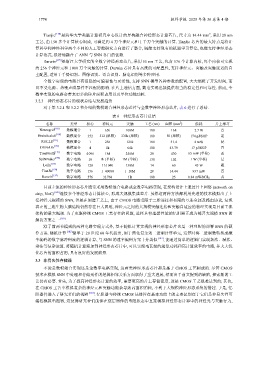

对于第 3.2.1 和 3.2.2 节介绍的数模混合神经形态芯片与全数字神经形态芯片, 表 6 进行了总结.

3.3 非易失性存储器

表 6 神经形态芯片总结

2

名称 类型 核心 神经元 突触 工艺 (nm) 面积 (mm ) 能耗 片上学习

[169]

Neurogrid 数模混合 1 65k 100M 180 168 2.7 W 否

[170]

BrainScaleS 数模混合 352 512 (单核) 130k (单核) 180 50 (单核) 174 pJ/SOP 是

[171]

ROLLS 数模混合 1 256 128k 180 51.4 4 mW 是

[172]

DYNAPs 数模混合 4 1k 64k 180 43.79 17 pJ/SOP 否

[173]

TrueNorth 数字电路 4 096 1M 256M 28 430 65 mW (单核) 否

[174]

SpiNNaker 数字电路 18 1k (单核) 1M (单核) 130 102 1 W (单核) 是

[176]

Loihi 数字电路 128 131 040 130M 14 60 45 W 是

[178]

TianJic 数字电路 156 1–40000 1–10M 28 14.44 937 mW 否

[179]

Darwin 数字电路 576 32 768 1B 180 25 0.84 mW/MHz 否

目前主流的神经形态芯片通常采用数模混合电路或全数字电路实现, 在架构设计上通过片上网络 (network on

chip, NoC) [180] 连接多个神经形态计算核心, 形成大规模集成芯片. 虽然这两种方法都利用先进的技术模拟出了上

亿神经元规模的 SNN, 但是在制造工艺上, 由于 CMOS 电路受限于二维连接和有限的互连金属及路由协议, 复现

真正的三维生物大脑结构仍然存在巨大困难, 神经元之间的大规模突触连接和突触自适应的物理实现是目前主流

架构的最大瓶颈. 为了克服传统 CMOS 工艺存在的问题, 选择具有理想性能的忆阻器正成为部署大规模 SNN 的

解决方案之一 [181] .

除了前两节提到的两种电路实现方式外, 基于随机计算实现的神经形态芯片也是一种理想的部署 SNN 的硬

件方案. 随机计算 [182] 最早于 20 世纪 60 年代提出, 用于简化复杂的二进制计算单元, 运算时将二进制数转换成概

率编码的数字脉冲码流的逻辑计算, 与 SNN 的速率编码方案十分类似 [183] , 能通过简单的逻辑门实现加法、减法、

乘法等复杂运算. 将随机计算添加到神经形态芯片中, 可以实现毫瓦级的超低功耗和高计算效率的电路, 并大大优

化芯片的面积占用, 具有良好的发展前景.

不论是数模混合实现还是全数字电路实现, 这两类神经形态芯片都是基于 CMOS 工艺制成的. 尽管 CMOS

技术在模拟 SNN 中处理和存储元件的逻辑相邻关系方面取得了重大进展, 然而出于前文提到的缺陷, 探索新的工

艺仍有必要. 首先, 为了提高神经形态计算的效率, 需要更高的片上存储密度, 这是 CMOS 工艺很难达到的; 其次,

在 CMOS 工艺中模拟复杂的神经元和突触功能会导致高面积消耗, 不利于大规模神经形态系统的搭建. 于是, 忆

阻器件进入了研究者们的视野 [184] . 忆阻器与传统 CMOS 晶体管在基本功能上的主要区别在于它们是非易失性可

编程模拟电阻器, 这使得研究者们能够在底层器件的电阻状态中直接模拟神经形态计算中的神经元与突触行为,