Page 366 - 《软件学报》2025年第4期

P. 366

1772 软件学报 2025 年第 36 卷第 4 期

获得最合适的性能与功耗配置将一直是该领域需要面对的问题. 当使用 FPGA 实现 SNN 时, 另一个挑战是确定适

当的模型和模型组合, 以及部署在逻辑阵列上的互连和架构问题, 以便网络可以进行训练和片上学习. 此外, 与

CPU 和 GPU 相比, FPGA 在算力上具有明显劣势, 因此在 FPGA 上实现 SNN 非常耗时. 最后, 由于 FPGA 的可编

程性相对较低 [163] , 缺乏诸如 TensorFlow, PyTorch 等软件开发框架的支持, 因此需要开发人员对硬件细节有更深

入的了解, 开发难度较高.

针对这些问题, 可以总结未来在 FPGA 平台上部署 SNN 的研究主题.

(1) 近似计算. 考虑到 FPGA 平台在资源方面的严格限制, 进一步压缩 SNN 模型中权重和参数的内存消耗是

非常有必要的. 近似计算方法是未来可以应用在基于 FPGA 的 SNN 加速器的技术, 文献 [164] 提出的近似乘法器

减少了 25%–53% 的 LUT 总使用量. 此外, 量化技术在 SNN 加速器上也具有十足的潜力.

(2) 自动模型生成. 网络架构搜索 (neural architecture search, NAS) 是近期研究的热点. 文献 [165] 探讨了 NAS

在 FPGA 上的应用, 这也可能是在 FPGA 平台上高效部署 SNN 的一种潜在的研究和应用思路.

(3) 在 FPGA 平台上提供 SNN 的开发框架. 为了降低 FPGA 开发的门槛, HLS (high-level synthesis) 高层次综

合工具 [166] 应运而生, 它提供了一种抽象层, 将高级语言代码转化为硬件级别的描述, 自动生成硬件电路, 使开发者

能够使用熟悉的高级语言进行硬件设计, 大大简化了 FPGA 的设计流程, 能有效降低 SNN 模型在 FPGA 平台部署

的门槛.

3.2 神经形态芯片

由于 SNN 在硬件电路实现时具有超低能耗的优势, 在过去 10 年中, 各类以 SNN 为原型的神经形态芯片不断

涌现. 与 ANN 缺乏生物可解释性不同, 神经形态芯片从大脑的结构和功能中汲取灵感, 其主体是一个类似于人脑

神经网络的近似 SNN. 与传统计算机取指-执行的循环工作方式不同, 神经形态芯片遵循并行工作和分布式处理机

制, 完成学习、记忆、推理等认知任务 [167] . 许多计算核心在芯片中同时工作, 模拟生物神经元的动力学行为, 通过

路由网络完成和其他计算核心的数据和与控制交互, 呈现去中心化的操作模式, 具有极高的并行性和内存访问效

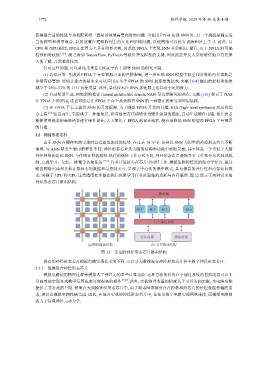

率, 突破了 CPU 和 GPU 这类通用处理器在执行深度学习任务时面临的功耗与内存瓶颈. 图 12 展示了两种常见的

神经形态芯片路由结构.

现有的神经形态芯片根据电路实现技术的不同, 可以分为数模混合神经形态芯片和全数字神经形态芯片.

路由器

核 0 核 1 核 2 … 核 n

片上通信系统

公共内存 周边外设

(a) 网状路由结构 (b) 公共路由结构

图 12 常见的神经形态芯片路由结构

3.2.1 数模混合神经形态芯片

模拟电路使用物理过程来模拟人工神经元的某些计算功能. 这种方法的优势在于通过系统的自然动态可以非

常高效地实现显式数学运算成本可能很高的操作 [168] . 此外, 实值物理变量的精度几乎可以达到无限, 为电路功能

提供了非常高的上限. 然而在大规模神经形态芯片中, 由于路由网络部分存在跨核和跨芯片的长程数据传输的需

求, 难以用模拟电路精确完成, 因此, 在混合实现的神经形态芯片中, 往往用数字电路实现网络连接, 而模拟电路则

致力于复现神经元动力学.