Page 365 - 《软件学报》2025年第4期

P. 365

俞诗航 等: 神经形态计算: 从脉冲神经网络到边缘部署 1771

文献 [137] 在 Spartan-6 FPGA 上建立了一个神经形态框架, 使双足、四足和六足的机器人能够自由运动, 可以与

多足机器人的 CPG 运动机制相结合.

在图像识别领域, 基于 FPGA 实现的 SNN 得到了大量的应用. 文献 [138] 在 Xilinx SPARTAN-6 FPGA 上实

现了一种同时利用基于事件和基于帧的处理方式的混合神经网络, 兼具 ANN 与 SNN 的特点, 在每帧仅需消耗 7 μJ

的情况下, 最终在 MNIST 数据集上获得了 97% 的准确率. 文献 [139] 在 Xilinx Zynq ZCU102 上高效部署了 SNN

模型. 该工作使用两种并行方法来提高数据重用率, 最终在 MNIST 数据集上达到了 98.94% 的准确率, 功耗比

GPU 实现方法低 22 倍, 速度比 CPU 实现方法快 41 倍. 文献 [140] 采用事件驱动 STDP 规则进行训练, 从输入模

式中学习各种特征, 并以无监督方式进行分类, 在 Stratix III FPGA 平台上实现了高能效的 SNN, 最终在 MNIST 数

据集上的准确率为 93%.

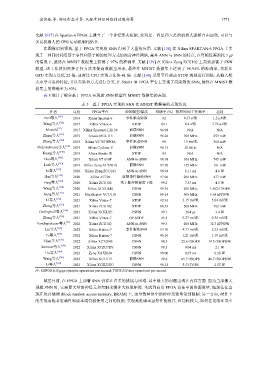

表 5 统计了部分基于 FPGA 实现的 SNN 模型在 MNIST 数据集的表现.

表 5 基于 FPGA 实现的 SNN 在 MNIST 数据集的表现情况

作者 年份 FPGA平台 SNN模型/算法 准确率 (%) 推理时间/工作频率 功耗

CSNN

Neil等人 [141] 2014 Xilinx Spartan-6 事件驱动SNN 92 0.53 s/张 1.2 μJ/张

Wang等人 [142] 2017 Xilinx Virtex-6 STDP 89.1 8.4 s/张 1.76 μJ/张

Mostafa [51] 2017 Xilinx Spartan6-LX150 前馈SNN 96.98 N/A N/A

Zhang等人 [143] 2019 Terasic DE2-115 前馈SNN 96.26 100 MHz 293 mW

Zhang等人 [144] 2019 Xilinx VC707 FPGA 事件驱动SNN 98 1.1 ms/张 360 mW

Abderrahmane等人 [145] 2019 Altera Cyclone V 前馈SNN 98.15 50 MHz N/A

Kuang等人 [140] 2019 Altera Stratix III STDP 93 N/A N/A

Guo等人 [146] 2019 Xilinx V7 690T ANN-to-SNN 98.98 100 MHz 745 mW

Losh等人 [147] 2019 Xilinx Zynq XC7Z010 前馈SNN 97.70 125 MHz 161 mW

Ju等人 [139] 2020 Xilinx Zynq ZCU102 ANN-to-SNN 98.94 6.11 ms 4.6 W

Han等人 [148] 2020 Xilinx ZC706 前馈事件驱动SNN 97.06 200 MHz 477 mW

Fang等人 [149] 2020 Xilinx ZCU102 基于脉冲的梯度下降 99.2 7.53 ms 4.5 W

Wang等人 [150] 2020 Xilinx XCVU440 CSNN 99.16 200 MHz 1.562 5 TOPS

Aung等人 [151] 2021 UltraScale+ VCU118 CSNN 99.14 500 MHz 5.64 kFPS/W

Li等人 [152] 2021 Xilinx Virtex-7 STDP 92.93 3.15 ms/张 5.04 mJ/张

Zheng等人 [153] 2021 Xilinx ZCU102 STDP 90.53 200 MHz 782 mW

Gerlinghoff等人 [154] 2021 Xilinx XCKU3P CSNN 99.1 294 μs 3.4 W

Zhang等人 [155] 2021 Xilinx Virtex-7 BP-STDP 95.3 0.27 ms/张 0.34 mJ/张

Panchapakesan等人 [53] 2022 Xilinx ZCU102 ANN-to-SNN 99.3 200 MHz 32.7 kFPS/W

Liu等人 [156] 2022 Xilinx Kintex-7 事件驱动SNN 97.70 4.17 ms/张 2.23 mJ/张

Ye等人 [157] 2022 Xilinx Kintex-7 CSNN 99.10 1.21 ms/张 1.19 mJ/张

Chen等人 [158] 2022 Xilinx XC7Z045 CSNN 98.5 22.6 GSOPS 19.3 GSOPS/W

Sommer等人 [159] 2022 Xilinx XCZU7EV 98.3 0.04 ms 2.1 W

Liu等人 [160] 2023 Zynq XA7Z020 CSNN 99.00 0.27 ms 0.28 W

Wang等人 [161] 2023 Xilinx KCU115 前馈SNN 99.4 65.7 GSOPS 41.7 GSOPS/W

Li等人 [162] 2023 Xilinx XCZU3EG CSNN 98.12 5.53 TOPS 2.55 W

注: GSPOS表示giga synaptic operations per second; TOPS表示tera operations per second

截至目前, 在 FPGA 上部署 SNN 仍存在许多的挑战与困难. 其中最大的问题出现在内存方面. 因为当部署大

规模 SNN 时, 它需要大量的神经元和突触来缓冲大权重矩阵. 考虑到商用 FPGA 设备中的资源数量, 瓶颈往往出

现在块存储器 (block random access memory, BRAM) 上, 这导致网络中的神经元数量受到限制. 另一方面, 硬件上

的实现面临着准确性和成本或资源使用之间的权衡. 实现高准确率虽然性能优异, 但功耗较大, 如何在边缘环境中