Page 485 - 《软件学报》2025年第8期

P. 485

3908 软件学报 2025 年第 36 卷第 8 期

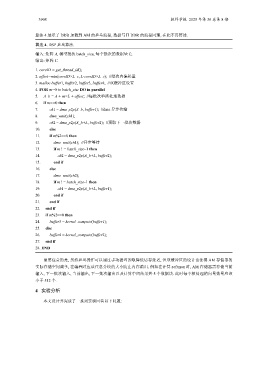

算法 4 展示了 DDR 加载到 AM 的乒乓流程, 数据写回 DDR 的流程同理, 在此不再赘述.

算法 4. DSP 乒乓算法.

输入: 矩阵 A, 模型批次 batch_size, 每个批次的数据量 L;

输出: 矩阵 C.

1. coreID = get_thread_id();

2. offset=min(coreID×L_c, L-coreID×L_c); //批次内偏移量

3. malloc buffer1, buffer2, buffer3, buffer4; //双缓冲区设置

4. FOR m=0 to batch_size DO in parallel

5. A_b = A + m×L + offset; //每批次单核处理数据

6. if m==0 then

7. ch1 = dma_p2p(A_b, buffer1); //dma 异步传输

8. dma_wait(ch1);

9. ch2 = dma_p2p(A_b+L, buffer2); //预取下一批次数据

10. else

11. if m%2==0 then

12. dma_wait(ch1); //异步等待

13. if m ! = batch_size–1 then

14. ch2 = dma_p2p(A_b+L, buffer2);

15. end if

16. else

17. dma_wait(ch2);

18. if m ! = batch_size–1 then

19. ch1 = dma_p2p(A_b+L, buffer1);

20. end if

21. end if

22. end if

23. if m%2==0 then

24. buffer3 = kernel_compute(buffer1);

25. else

26. buffer4 = kernel_compute(buffer2);

27. end if

28. END

需要注意的是, 虽然乒乓操作可以通过手动循环预取降低访存延迟, 但双缓冲区的设计也使得 AM 存储器的

实际存储空间减半, 在编程时应该注意分块的大小防止内存溢出. 例如在计算 softmax 时, AM 存储器需存储当前

输入, 下一批次输入, 当前输出, 下一批次输出以及计算中间结果共 5 个数据块. 此时每个核处理的向量数量应该

小于 512 个.

4 实验分析

本文设计并完成了一系列实验回答以下问题: