Page 75 - 《软件学报》2024年第6期

P. 75

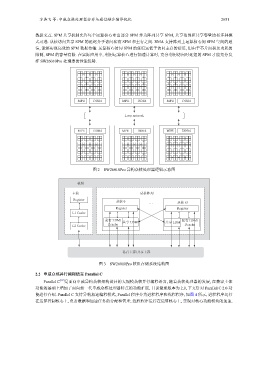

方燕飞 等: 申威众核处理器访存与通信融合编译优化 2651

数据交互. SPM 共享机制允许每个运算核心拿出部分 SPM 作为阵列共享 SPM, 共享范围和共享容量均有多种模

式可选. 从核访问共享 SPM 的延迟介于访问私有 SPM 和主存之间. RMA 支持阵列上运算核心间 SPM 空间的通

信, 能够实现高效的 SPM 数据传输. 运算核心访问 SPM 的延迟远低于访问主存的延迟, 但由于芯片面积及功耗的

限制, SPM 的容量有限. 在实际应用中, 利用运算核心进行加速计算时, 充分利用访问时延短的 SPM 才能充分发

挥 SW26010Pro 处理器的性能优势.

MPE DDR4 MPE DDR4 MPE DDR4

Loop network

MPE DDR4 MPE DDR4 MPE DDR4

图 2 SW26010Pro 异构众核处理器逻辑示意图

核组

从核阵列

主核 图 3 SW26010Pro

Register

从核 0 … 从核 63

Register Register

L1 Cache

私有 LDM/ 私有 LDM/

Dcache 共享 LDM 共享 LDM Dcache

L2 Cache

私有主存/共享主存

核组存储系统结构图

2.2 申威众核并行编程语言 Parallel C

Parallel C [12] 是面向申威异构众核架构设计的大规模众核并行编程语言, 随着众核处理器的发展, 在兼容主体

功能的基础上增加了面向新一代申威众核处理器特点的功能扩展, 目前最新版本为 2.0, 下文针对 Parallel C 2.0 功

能进行介绍. Parallel C 支持异构加速编程模式, Parallel 程序分为进程程序和线程程序, 如图 4 所示, 进程程序运行

在运算控制核心上, 负责数据和加速任务的分配和管理; 线程程序运行在运算核心上, 实现对核心功能模块的加速.