Page 73 - 《软件学报》2024年第6期

P. 73

方燕飞 等: 申威众核处理器访存与通信融合编译优化 2649

高性能计算 (HPC) 已经迈入 E 级 (E 为超级计算机运算单位, 意为每秒百亿亿次) 时代. 众核处理器 (many-

core processor) [1−4] 凭借超高的性能功耗比和性能面积比成为超算领域的主流处理器架构, 典型的高性能计算众核

处理器有 NVIDIA、AMD 和 Intel 公司的 GPGPU、申威新一代众核处理器以及飞腾众核处理器 GX64-DSP 等.

随着工艺的不断发展, 众核处理器片上规模不断扩大, 核心数量不断增加, 众核计算能力不断提升, 但这并不意味

着总是能带来众核应用程序的性能提升. 一方面, 程序员需要挖掘充分的应用并行性才能充分利用众多计算核心

的并行性. 另一方面, 随着计算能力的不断提升, 众核访存能力提升却有限, 随着应用类型越来越多样化, 许多应用

在众核上的计算遇到“访存墙”问题.

为应对“访存墙”挑战, 申威众核处理器设计了具有片上通信功能的从核多级存储层次结构, 片上 SRMA 采用

便签式存储器 SPM (scratch pad memory) 和 Cache 的混合结构, 且两者容量灵活可配. 在片上高速网络的支持下,

片上 SPM 不仅可以配置为单个核心私有模式, 还可以配置成多核心共享等多种模式, 同时支持主存与 SPM 间的

DMA、不同核心 SPM 间的 RMA 通信等批量数据传输机制. 虽然引入片上 Cache 结构使众核编程工作在相对只

[5]

有 SPM 结构时更容易, 但新一代申威众核处理器 SW26010Pro 只支持 1 级数据 Cache, 一旦发生 Cache 不命中,

将直接产生高延迟的主存访问. 而即使是具有较好 Cache 局部性的数组连续访问, 使用 Cache 和 SPM+DMA 编程

获取制约关系明确

在性能上也有较大差距, 经过在 SW26010Pro 上的实测发现, 前者性能只有后种访问方式的 80%. 此外, 片上

RMA 通信机制也是宝贵的资源, 高剑刚等人 [6] 通过所提出的面向申威众核处理器存储层次特点的 PLAN 并行计

算模型, 证明了充分利用高速私有存储层 SPM 以及片上 RMA 通信机制可以很好地提高片上数据的利用率, 减少

对主存访问带宽的需求. 为追求极致性能, 申威超算上的高性能应用事实上也大多采用 SPM 结构进行深度优化实现.

虽然在 SW26010Pro 上使用 SPM 方式编程能够给程序优化带来更大的灵活性和可控性, 应用开发人员可以充

分利用运算核心间的 SPM 访问、RMA 通信等机制提升片上核心数据的重用率, 可以更好挖掘程序性能优化空间.

但与此同时, 完全由软件管理的 SPM 以及片上 RMA 通信机制也给众核应用程序优化和移植带来了很多挑战. 主要

难点有两个方面: 一方面, 程序开发人员不仅要掌握应用数据访问特征, 还需要深入掌握目标处理器的存储层次特

征, 才能通过算法设计与程序优化来挖掘利用硬件结构优势. 另一方面, 众核片上存储层次结构在不断发展, 不同类

型的处理器, 同一类型不同代系的处理器, 其片上存储结构和容量都不尽相同, 在某一型号的众核处理器上深度优化

的众核并行应用程序, 难以直接在另一款众核处理器上运行, 简单的移植改造也难以获得理想性能. 由于 SPM 完全

由软件管理, 以 Cache 优化为核心的传统编译优化技术也不再适用, 并行编程语言编译需要针对众核混合片上存储

层次的结构特点开展研究, 从编程、编译层面提供更多技术支持, 帮助程序开发人员减轻程序开发与优化负担.

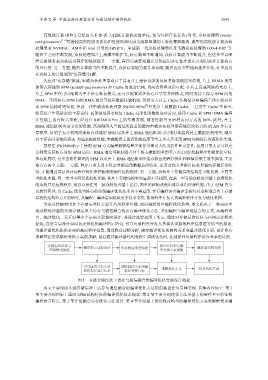

为充分挖掘利用片上存储层次特点提升应用程序性能, 同时减轻用户编程优化负担, 本文提出了一种面向申

威众核处理器的多级存储层次上访存与通信融合的访存编译优化方法, 采用编程与编译相结合的方式, 从编程语

言、编译优化、运行时等多个层面开展协同设计, 其设计流程如图 1 所示, 通过对存储层次特征与应用访存模式

提炼, 在语言层设计面向访存优化的编译指示语句, 引导应用程序开发人员将其掌握的程序信息进行恰当的描述,

为编译器优化提供必要的高层程序信息; 通过收益建模分析, 确定编译优化的制约关系变量及优化目标; 设计贪心

求解算法完成循环变换方案的求解; 最后通过编译器代码变换生成优化代码, 达到提升应用程序访存效率的目的.

存储层次特征与 编译指示功能设计 缓冲区管理与循 编译器代码变换

应用模式提炼 优化收益模型构建 环变换方案求解

引导应用开发人员

提供程序高层信息 循环变换目标 求解优化方案 优化代码生成

图 1 多级存储层次上访存与通信融合的编译优化方法设计流程

本文主要论述多级存储层次上访存与通信融合的编译优化方法的思路设计与具体实现. 具体内容如下: 第 1

节主要介绍国际上面向 SPM 结构特征的编译优化技术现状. 第 2 节主要介绍优化方法所基于的硬件平台特征和

编程语言特点. 第 3 节介绍融合访存优化方法设计. 第 4 节介绍基于优化收益模型的编译优化方案求解框架及编