Page 326 - 《软件学报》2021年第9期

P. 326

2950 Journal of Software 软件学报 Vol.32, No.9, September 2021

的占用而带来性能优化.这部分的优势是因为分子动力学模拟程序是时间演化类以及高频迭代类程序的典型

代表,不同处理器核间频繁大量的数据交换导致此类程序对延迟较敏感,网络延迟对算法的性能影响较大.因

此,神威系统上单进程通信的优化算法主要针对对异构架构下类似的延迟敏感及通信受限类应用的优化提供

了参考.

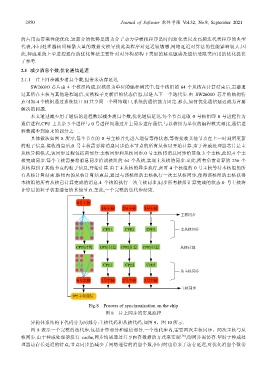

2.1 减少消息个数,优化通信延迟

2.1.1 片上同步减少消息个数,但带来访存延迟

SW26010 芯片由 4 个核组构成,以核组为单位的编程模式中,每个核组的 64 个从核在计算结束后,需要通

过其所在主核与其他进程通信,交换粒子更新后的状态信息,以进入下一个迭代步.由 SW26010 芯片的结构特

点可知:4 个核组通过系统接口 SI 共享同一个网络端口,系统的通信能力固定.那么,如何优化通信延迟成为首要

解决的问题.

本文通过减少用于通信的进程数以减少消息个数,优化通信延迟.每个节点选取 0 号核组即 0 号进程作为

通信进程,CPU 上其余 3 个进程与 0 号进程间通过片上同步进行通信.与以核组为单位的编程模式相比,通信进

程数减少到原来的四分之一.

具体做法如图 8 所示,每个节点的 0 号主核首先进入通信等待状态,等待接收其他节点在上一时刻所更新

的粒子信息.接收消息后,0 号主核需要将消息同步给本节点的所有从核以开始计算.由于神威处理器芯片是主

从核异构模式,该同步过程包括两部分:主核同步和从核同步.0 号主核将消息同步给其他 3 个主核,此时,4 个主

核完成同步.每个主核需要将消息同步给该核组的 64 个从核,实现主从核的同步.至此,所有负责计算的 256 个

从核得到了其他节点的粒子信息,开始计算.由于主从核的异步执行,此时 4 个核组的 0 号主核等待本核组的所

有从核计算结束.核组内的从核计算结束后,通过与该核组的主核执行一次主从核同步,使得该核组的主核获得

本核组的所有从核已计算完成的消息.4 个核组执行一次主核同步,同步所有核组计算完成的状态.0 号主核将

计算后的粒子状态通信给其他节点.至此,一个完整的迭代步结束.

0号主核

1号主核 2号主核 3号主核

主核同步

CPE1 CPE2 CPE3 主从核同步

... ... ...

CPE0计算 CPE1计算 CPE2计算 CPE3计算 从核计算

... ... ... CPE1 CPE2 CPE3

从主核同步

0号主核 1号主核 2号主核 3号主核

主核同步

0号主核通信

Fig.8 Process of synchronization on the chip

图 8 片上同步的实现流程

异构体系结构下代码分为两部分:主核代码和从核代码,如图 9、图 10 所示.

图 8 表示一个完整的迭代步,包括计算部分和通信部分.一个迭代步内,需要两次主核同步、两次主核与从

核同步.由于神威处理器没有 cache,同步均需通过共享内存数据的方式来实现 [16] ,即同步需访存.掣肘于神威处

理器访存长延迟的特点,节点同步虽减少了网络通信的消息个数,但同时也带来了访存延迟,对优化消息个数带