Page 43 - 《软件学报》2021年第8期

P. 43

水超洋 等:国产异构系统上 HPL 的优化与分析 2325

Fig.5 Heterogeneous acceleration framework HPCX

图 5 异构加速框架 HPCX

4 性能测试与分析

我们实现了包括国产加速器和 NVIDIA GPU 两种异构平台上的粗粒度版本 HPL 和多线程细粒度版本

HPL,在国产加速器和 NVIDIA 两个平台上进行了测试.在 NVIDIA 平台上,我们将我们实现的两个版本的 HPL

与开源成果三阶段流水线版本 HPL 以及目前 NVIDIA 平台上效率最高的 NVIDIA 官方非开源程序 nvhpl 进行

了对比.在国产加速器平台上,我们在曙光 E 级超算原型机的 512 个节点上进行大规模扩展性测试.

4.1 实验平台简介

表 2 给出了我们实验平台的信息.在两种平台上,单个节点内处理器与加速器都通过 PCIe 3.0 总线连

接.NVIDIA 平台上只有一个节点,配有两张 P100 显卡.国产加速器平台上有多个节点,每个节点上装有一个国产

加速器,节点之间采用 100Gb/s 的 EDR 网络连接.

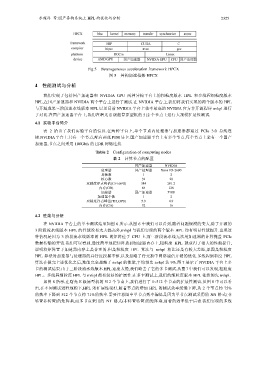

Table 2 Configuration of computing nodes

表 2 计算节点的配置

国产加速器 NVIDIA

处理器 国产处理器 Xeon E5-2690

封装数 1 2

核心数 32 28

双精度浮点峰值(GFLOPS) 384 291.2

内存(GB) 64 128

加速器 国产加速器 P100

加速器个数 1 2

双精度浮点峰值(TFLOPS) 5.9 4.9

内存(GB) 32 16

4.2 性能与分析

在 NVIDIA 平台上的单卡测试结果如图 6 所示.从图 6 中我们可以看到,随着问题规模的变大,除了开源的

3 阶段流水线版本 HPL 的性能没有太大提高外,nvhpl 与我们实现的两个版本 HPL 均有明显性能提升.出现这

种情况是因为 3 阶段流水线版本的 HPL 的矩阵位于 CPU 上,而三阶段流水线无法用加速器的计算掩盖 PCIe

数据传输的开销.我们可以看到,通过简单地把矩阵放到加速器内存上,粗粒度 HPL 就获得了很大的性能提升,

说明将矩阵置于加速器内存上是合理的.但是粗粒度 HPL 算法与 nvhpl 相比还是有较大差距,原因是粗粒度

HPL 算法对加速器与处理器的并行度挖掘不够,以及忽略了行交换中网络通信开销的优化.多线程细粒度 HPL

算法在做完上述优化之后,性能完全超越了 nvhpl 的性能,平均领先 nvhpl 达 9%.图 7 展示了 NVIDIA 平台上多

卡的测试结果.由于三阶段流水线版本 HPL 速度太慢,我们略去了它的多卡测试.从图 7 中我们可以发现,粗粒度

HPL、多线程细粒度 HPL 与 nvhpl 都有较好的扩展性.在多卡测试上,我们的细粒度版本 HPL 依然领先 nvhpl.

如图 8 所示,在曙光 E 级原型机的 512 个节点上,我们进行了 1~512 个节点的扩展性测试.从图 8 中可以看

出,在不同测试进程规模下,HPL 的扩展性很好,随着节点的增加 HPL 的测试效率缓慢下降,从 2 个节点约 75%

的效率下降到 512 个节点约 71%的效率.需要注意图中单节点效率偏低是因为单节点测试采用的 NN 格式(非

转置非转置)的矩阵乘,而多节点采用的 NT 格式(非转置转置)的矩阵乘,前者的效率低于后者.我们实现的多线