Page 41 - 《软件学报》2021年第8期

P. 41

水超洋 等:国产异构系统上 HPL 的优化与分析 2323

3 多线程细粒度 HPL 算法设计及实现

在已有的文献中,LU 分解的 4 个子过程,panel 分解,panel 广播,行交换和尾矩阵的更新都是顺序执行的.在

过去纯 CPU 时代,由于尾矩阵更新占据了 90%以上的时间,HPL 的效率主要由 DGEMM 的效率决定,其他 3 个

[5]

子过程对性能的影响不大.此时这种顺序执行 4 个步骤,或者通过简单的 look-ahead 算法 实现粗粒度流水的算

法也能取得很好的效果.但是对于国产处理器-国产加速器异构架构,由于国产加速器计算能力与国产处理器的计

算能力存在 1~2 个数量级的差距,尾矩阵更新的时间占比减少到了 50%左右,此时 panel 分解,panel 广播和行交换

对性能的影响就不能忽略.在这样的背景下,探索一个新的细粒度流水算法用 update 的有用计算去掩盖 panel 分

解、panel 广播和行交换的开销对于提升 HPL 的效率,充分发挥国产加速器的强大计算能力显得尤为重要.

3.1 多线程细粒度HPL算法的设计

HPL 耗时最多的计算是尾矩阵 A 22 更新的矩阵乘法计算,异构 HPL 算法加速的核心是利用国产加速器加速

矩阵乘法.传统的 CPU-加速器异构 HPL 算法通过把 panel 分解的结果 L 11 ,U 12 ,L 21 矩阵拷贝到加速器内存,同时

j

将更新前的尾矩阵 A 22 拷贝到加速器内存,利用加速器求解 U 12 和更新尾矩阵,将更新后的尾矩阵 A 拷贝回

22

CPU 内存 [17] .这种做法将系数矩阵放在 CPU 端内存中,每次调用加速器的 DGEMM 都需要把数据通过 PCIe 拷

贝到加速器内存,在完成计算后又需要把结果矩阵拷贝回 CPU 内存.在文献[6]中通过三阶段流水的办法用加速

器上的计算来掩盖 PCIe 数据传输的开销,但是加速器算力增加的速度远远高于 PCIe 带宽的增加速度,它们之

间越来越大的差距使得加速器计算的时间无法掩盖 PCIe 传输的时间.为了解决这个问题,我们将系数矩阵放在

国产加速器的内存上,这样就避免了国产处理器和国产加速器之间大量的数据交换.只需要在国产处理器做

panel 分解之前,从国产加速器把 panel 需要的 NB 列数据拷贝回来就可以了.假设当前迭代中剩余待求解系数矩

阵大小为 n× (n + 1) ,原来粗粒度并行的算法中,我们需要通过 PCIe 移动 8(2 n× ×× (n + 1) n NB+ × + NB× (N + 1))

字节的数据,现在只需要移动 8(2 nNB× × × + NB× (n + 1)) 字节数据,通过 PCIe 的数据传输量大大减少了.这个版

本的 HPL 算法我们称为粗粒度 HPL 算法.

粗粒度 HPL 算法存在两个问题导致其不能取得很高的性能.一个问题是由于尾矩阵更新时间占比减少,行交

换的网络传输的开销显得越来越大.另一个问题是通过简单使用国产加速器的异步流机制让国产处理器端的

panel 分解和国产加速器端的 update 并行,国产处理器与国产加速器只有很弱的并行工作的效果,大部分时间国产

处理器与国产加速器都是串行执行,这造成了国产加速器大量的空闲等待时间.为了解决这两个问题,我们设计了

一种国产处理器-国产加速器异构多线程细粒度流水算法.我们通过对数据依赖的分析发现尾矩阵更新与行交换

在列与列之间是没有数据依赖的.

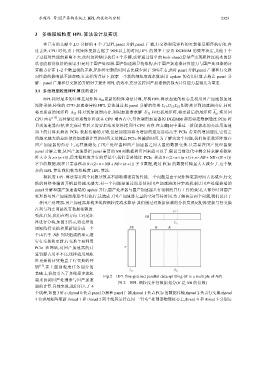

受此启发,我们在列方向上对尾矩

阵进行分块,如图 2 所示,将完整的

尾矩阵行交换和更新划分成一个

个由若干 NB 列块组成的单元进

行行交换和更新.行交换主要利用

PCIe 和网络,对国产加速器的计

算资源占用率不高,这样就用尾矩

阵更新的计算掩盖了行交换的开

销 [17] .在上面细粒度任务划分的

基础上,我们引入了多线程多流机

Fig.2 HPL fine-grained parallel data splitting (K is a multiple of NB)

制来协调国产处理器与国产加速

图 2 HPL 细粒度并行数据划分(K 是 NB 的倍数)

器的计算.具体来说,我们引入了 4

个线程,如图 3 所示,thread 0 负责 panel 分解和 panel 广播,thread 1 负责 PCIe 的数据传输,thread 2 负责行交换,thread

3 负责尾矩阵更新.thread 1 和 thread 2 两个线程运行在同一个国产处理器物理核心上,thread 0 和 thread 3 分别运