Page 107 - 《软件学报》2020年第10期

P. 107

娄文启 等:一种神经网络指令集扩展与代码映射机制 3083

5 实验及结果

为了验证所提出的专用指令的有效性,我们在 FPGA 平台上构建了包含该指令集扩展的基于 RISC-V 架构

的处理器核.在此基础上,使用 AlexNet、VGG16 两种不同规模的卷积神经网络进行评测,并将该原型系统与

Cambricon、CPU、GPU 和其他 FPGA 加速器进行对比分析.

5.1 实验方法

(1) 原型系统的 FPGA 实现

我们使用 ZC702 开发板作为实验平台,该平台为嵌入式 FPGA 平台,其中,包含了一块 XC7Z020 FPGA 芯片

和 1GB DDR3 板载内存,可提供 4.2GB/s 的片外数据存取带宽.RISC-V 基础内核及矩阵单元的控制使用硬件描

述语言 Verilog 来完成,矩阵单元中的子计算单元设计则通过 Xilinx Vivado HLS 2017.4 高层次综合工具完成,

完整的硬件工程通过 Xilinx Vivado 2017.4 集成开发环境进行综合和实现.

(2) CPU 测试基准

我们使用 Caffe 深度学习框架(CPU-only)在 CPU 平台上部署了两种目标网络模型.CPU 配置为 Intel

i7-4790K,其中包含了 4 物理核心,最大线程数为 8,工作频率为 4GHz,并配有 16GB DDR3 内存.

(3) GPU 测试基准

GPU 版本的测试仍然通过 Caffe 深度学习框架(GPU-only)并通过 CuDNN5.1 加速库在 GPU 平台上部署两

种目标网络模型.GPU 配置为 NVIDIA Tesla K40C,其最大可支持 2 880 个硬件线程,工作频率为 745~875MHz,

并配有 12GB GDDR5 显存.

5.2 实验结果

在本节中,我们首先报告了原型系统在 FPGA 平台上的资源消耗和功耗,然后围绕代码密度、性能及能效 3

个方面将该设计与 Cambricon、CPU、GPU 以及以往基于 FPGA 的加速器进行对比分析.

通过查看原型系统在 Vivado 工具中的部署报告,我们获得了其在目标平台的各项资源消耗以及 FPGA 的

功耗,见表 2.

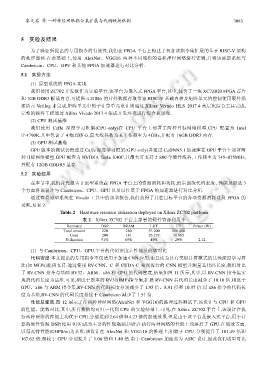

Table 2 Hardware resource utilization deployed on Xilinx ZC702 platform

表 2 Xilinx ZC702 平台上部署的硬件资源利用率

Resource DSP BRAM LUT FF Power (W)

Total amount 220 280 53 200 106 400

Used 200 181 26 177 30 665

Utilization 91% 65% 49% 29% 2.12

(1) 与 Cambricon、CPU、GPU 平台的代码密度、性能及能效对比

代码密度.本文提出的专用指令不仅适用于加速 CNN 应用,而且还为具有类似计算模式的其他深度学习算

法(如 MLPs)提供支持.通过使用 RV-CNN、C 和 CUDA-C 实现流行的 CNN 模型并测量其代码长度,我们对比

了 RV-CNN 指令与基础 RV32、ARM、x86 和 GPU 的代码密度,结果如图 11 所示,其中,以 RV-CNN 指令集实

现的代码长度为基准.可见,相比于原本的 RV32(IMF)指令集,扩展 RV-CNN 后代码长度减少了 10.10 倍.相比于

GPU、x86 与 ARM 指令集,RV-CNN 的代码长度分别减少了 1.95 倍、8.91 倍和 10.97 倍.以 x86 指令的代码长

度为基准,RV-CNN 的代码长度相比于 Cambricon 减少了 1.51 倍.

性能及能效.图 12 展示了在两种神经网络(AlexNet 和 VGG16)的推理过程测试下,该设计与 CPU 和 GPU

的性能、能效对比,其中,所有数值均可归一化到 CPU 的实验结果上.可见,在 Xilinx ZC702 平台上,该设计在执

行两种网络的性能上均优于 CPU,分别达到 2.64 倍和 4.23 倍的加速效果.但是由于该平台是嵌入式平台,用于计

算的硬件资源 DSP(使用 91%)成为主要的性能瓶颈,因此在执行两种网络的性能上均落后于 GPU.在能效方面,

以每瓦特性能(GOPS/w)为基准,该设计在 AlexNet 和 VGG-16 的推理上,相较于 CPU 分别提升了 101.49 倍和

167.62 倍;相较于 GPU 分别提升了 1.06 倍和 1.40 倍.由于 Cambricon 加速器为 ASIC 设计,因此我们这里对比