Page 63 - 《软件学报》2025年第9期

P. 63

3974 软件学报 2025 年第 36 卷第 9 期

2.1 RISC-V 架构硬件特性

近年来, RISC-V 架构迅速发展, 从最初的学术研究指令集逐渐演变为在工业界被广泛应用的流行架构 [12] . 随

着 RISC-V 的普及, 业界对将其他架构中的先进技术适配到 RISC-V 的兴趣也在不断增加. 例如, Arm64 [21] 和

x86 [22] 架构早已实现了特定的硬件来辅助虚拟化. 在近年来, RISC-V 的虚拟化扩展 (hypervisor extension,

H-extension) 也正式通过并纳入了特权架构规范 [23] . 这一扩展定义了可以在处理器核心中实现的硬件功能, 以减少

虚拟化的开销并简化 hypervisor 的实现. RISC-V 在初期并没有类似的硬件支持, 因此, 像 RVirt [18] 这样的

hypervisor 只能依赖于陷入-模拟机制, 通过特权模式来实现虚拟化分离, 这意味着虚拟化的所有处理都必须由软

件独立完成. 与传统架构相比, RISC-V 架构拥有全新的特权级模型和硬件特性, 因此在虚拟化技术的研究和应用

中, 应当充分利用这些特性, 以实现 RISC-V 定制的技术实现.

2.1.1 特权级模型

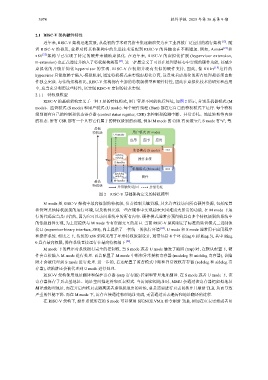

RISC-V 的基础架构定义了一种 3 层的特权模式, 用于管理不同的执行环境, 如图 2 所示, 分别是机器模式 (M

mode)、监督模式 (S mode) 和用户模式 (U mode). 每个硬件线程 (Hart) 都在它自己的特权模式下运行. 每个特权

级别都有自己的控制和状态寄存器 (control status register, CSR) 来控制和检测中断、异常委托、地址转换等内容

的状态. 所有 CSR 都有一个具有它们属于的特权级别的前缀, 例如 M mode 的 CSR 有前缀“m”, S mode 有“s”, 等.

最低

特权级 用户模式 (U mode)

U-handler

应用 应用 应用

监督模式 (S mode) sret

sedeleg

sideleg

Trap 操作系统

S-handler

Trap

机器模式 (M mode) mret

medeleg

mideleg 固件

最高 M-handler

特权级 异常触发/返回 异常委托

图 2 RISC-V 基础架构定义的特权模型

M mode 是 RISC-V 架构中最高级别的特权级, 负责控制关键资源, 其允许直接访问所有硬件资源, 包括配置

和管理其他特权级别的运行环境, 以及软件完成一些在硬件中实现起来太困难或太昂贵的功能. 在 M mode 下运

行的代码应当是可信的, 因为它可以访问系统中的所有内容. 硬件模式通常会预留给具有多个特权级别的系统中

的低级固件实现, 为上层提供与 M mode 专有资源交互的接口. 当前 RISC-V 架构制定了标准的监督模式二进制值

接口 (supervisor binary interface, SBI), 向上提供了一套统一的执行环境 [24] . U mode 和 S mode 通常用于应用程序

和操作系统. 相比之下, 传统的 x86 架构采用了环形特权级别设计, 通常包括 4 个环 (Ring 0 到 Ring 3), 其中 Ring

0 具有最高权限, 操作系统直接运行在最高特权级下 [22] .

M mode 下的程序对系统拥有完全的控制权. 当 S mode 或者 U mode 触发了陷阱 (trap) 时, 在默认配置下, 硬

件会直接陷入 M mode 进行处理. 而若配置了 M mode 中断和异常授权寄存器 (medeleg 和 mideleg 寄存器), 该陷

阱才会被代理到 S mode 进行处理. 进一步的, 若还配置了监督模式中断和异常授权寄存器 (sedeleg 和 sideleg 寄

存器), 该陷阱还会被代理到 U mode 进行处理.

RISC-V 架构使用地址翻译和保护寄存器 (satp 寄存器) 控制和管理地址翻译. 在 S mode 或者 U mode 下, 该

寄存器保存了页表基地址、地址空间描述符和页表模式. 当访问虚拟地址时, MMU 会通过该寄存器把虚拟地址

翻译成物理地址. 而在开启内核页表隔离或者虚拟机退出的时候, 总是需要进行页表切换并且刷新 TLB, 从而导致

严重的性能下降. 而在 M mode 下, 访存直接通过物理地址完成, 无需通过页表遍历和地址翻译的过程.

在 RISC-V 架构下, 操作系统所在的 S mode 可以使用 SFENCE.VMA 指令刷新 TLB, 例如在页表更新或者切