Page 276 - 《软件学报》2020年第11期

P. 276

李威威 等:基于硬件分支信息的 ROP 攻击检测方法 3591

ROP gadgets-chain:

... ... ... ... ...

Gadgets*n

检测触发点 ret ret ret ret syscall

硬件支持 LBR 分支 BPU 分支预测失败 劫持系统调用

跳转信息

PMU 触发 PMI 中断

常规 ROP 系统调用

检测信息来源

应用内存 攻击检测 参数检测 硬件流程

指令信息

软件流程

ROP 攻击检测

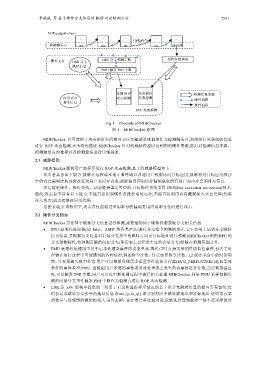

Fig.1 Principle of MIBChecker

图 1 MIBChecker 原理

MIBChecker 以可能用于攻击的所有间接分支以及敏感系统调用作为检测触发点,利用运行时获取的信息

进行 ROP 攻击检测.本节将先描述 MIBChecker 针对的威胁模型以及利用的硬件资源,然后对检测信息来源、

检测触发点的选择以及检测算法进行详细描述.

2.1 威胁模型

MIBChecker 面向用户态程序进行 ROP 攻击检测,基于的威胁模型如下.

攻击者具备如下能力:能够在远程或本地正常终端以普通用户权限访问目标应用;能够利用目标应用程序

中的内存漏洞读取或修改任意用户态内存内容;能够通过应用内存漏洞获取所有用户态内存空间排布信息.

但是假定硬件、操作系统、动态链接器是可信的,目标操作系统支持 DEP(data execution prevention)技术.

因此,攻击者不具备以下能力:不能直接控制硬件及操作系统运行;不能直接利用内存漏洞插入恶意代码(代码

注入攻击)或直接修改应用代码.

总的来说,在该模型下,攻击者仅能通过应用本身的漏洞复用应用本身代码进行攻击.

2.2 硬件分支信息

MIBChecker 方法基于硬件分支信息进行检测,需要借助如下硬件资源获取分支相关信息.

• BPU:是现代处理器(如 Intel、AMD 等各类产品)进行分支指令预测的单元.它主要用于记录分支跳转

历史信息,并根据历史信息对后续分支指令的跳转方向及目标地址进行预测.MIBChecker 利用 BPU 的

分支预测特性,将预测正确的间接分支(即历史上已经发生过的合法分支)排除在检测范围之外.

• PMU:是现代处理器中用于记录处理器事件的功能单元.现代 CPU 支持大量的性能监控事件,包含了处

理器在运行过程中可能遇到的各种情形,例如指令计数、浮点运算指令计数、L2 缓存未命中的时钟周

期、分支预测失败事件等.用户可以根据具体需求设置事件选择寄存器(IA32_PERFEVTSEL)选取需要

采样的事件类型.PMU 会根据用户所选的事件类型对处理器上发生的该事件进行计数,当计数器溢出

时,可以触发 PMI 中断,用户可以在中断处理过程中进行相关处理.MIBChecker 利用 PMU 采样预测失

败的间接分支事件触发 PMI 中断作为检测点进行 ROP 攻击检测.

• LBR:是 x86 架构中提供的一组用于记录和追踪程序最近的若干次分支跳转信息的循环寄存器组,它

们会记录跳转分支指令的地址信息{from_ip,to_ip},即分别对应于跳转源地址和目标地址.这些寄存器

的数量与处理器的微架构相关.另外,LBR 寄存器具备过滤功能,能够选择性地滤掉一些不需采样的分