Page 39 - 《软件学报》2020年第9期

P. 39

2660 Journal of Software 软件学报 Vol.31, No.9, September 2020

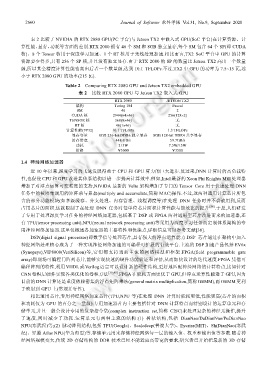

表 2 比较了 NVIDIA 的 RTX 2080 GPU(PC 平台)与 Jetson TX2 中嵌入式 GPU(SoC 平台)在计算资源、计

算性能、显存、功耗等方面的差别.RTX 2080 拥有 46 个 SM 和 8GB 独立显存,每个 SM 包含 64 个 SP(即 CUDA

核)、8 个 Tensor 核用于深度学习加速、1 个 RT 核用于光线处理加速.相比而言,TX2 SoC 平台中 GPU 的计算

资源要少得多,只有 256 个 SP 核,并且没有独立显存.由于 RTX 2080 的 SP 的数量比 Jetson TX2 高出一个数量

级,所以其全精度计算性能也高出后者一个数量级,达到 10.1 TFLOPs.不过,TX2 中 GPU 的功率为 7.5~15 瓦,远

小于 RTX 2080 GPU 的功率(215 瓦).

Table 2 Comparing RTX 2080 GPU and Jetson TX2 embedded GPU

表 2 比较 RTX 2080 GPU 与 Jetson TX2 嵌入式 GPU

RTX 2080 JETSON TX2

架构 Turing 104 Pascal

SM 46 2

CUDA 核 2944(64×46) 256(128×2)

TENSOR 核 368(8×46) 无

RT 核 46(1×46) 无

计算性能(FP32) 10.1 TFLOPs 1.3 TFLOPs

显存容量 8GB 256-bit DDR6 独立显存 8GB 128-bit DDR4 共享显存

访存带宽 448 GB/s 59.7GB/s

功耗 215W 7.5W/15W

价格 Ұ5000 Ұ3500

1.4 神经网络加速器

近 10 年以来,深度学习的飞速发展得益于 CPU 和 GPU 算力的巨大进步.反过来,DNN 计算时的高负载特

性,也促使 CPU 和 GPU 改进其体系结构以进一步提高计算效率.例如,Intel 最新的 Xeon Phi Knights Mill 处理器

增加了对浮点运算可变精度的支持,NIVIDA 最新的 Volte 架构增加了专门的 Tensor Core 用于快速处理 DNN

任务中的被密集调用的矩阵乘与累加(multiply and accumulate,简称 MAC)操作.不过,这两种通用计算芯片所包

含的部分功能模块(如多级缓存、分支处理、内存管理、线程调度等)在处理 DNN 任务时并不会被用到,反而

占用芯片的面积,这就限制了在处理 DNN 任务时每单位芯片面积计算性能与能效比的提升 [38] .于是,人们研发

了专用于处理深度学习任务的神经网络加速器,包括基于 DSP 或 FPGA 两种通用型芯片改进而来的加速器,还

有 TPU(tensor processing unit),NPU(neural network processing unit)等采用为深度学习任务而定制体系架构的专

用神经网络加速器.这里仅概述各加速器的主要特性和优缺点,详细信息可以参考文献[38].

DSP(digial signal processor)即数字信号处理芯片,具有强大的浮点运算能力.DSP 芯片通过在架构中加入

神经网络处理核心成为了一种实现神经网络加速的可编程可扩展的有效平台.主流的 DSP 加速产品包括 EV6x

(Synopsys),VIP8000(VeriSilicon)等,它们都支持当前主流的网络模型和框架.FPGA(field programmable gate

array)即现场可编程门阵列芯片,能够实现快速的硬件功能验证和评估,从而加快设计的迭代速度.FPGA 凭借可

编程阵列的特性,利用 VHDL 或 Verilog 语言可以设计新的硬件结构,更好地匹配神经网络的计算特点,比如针对

CNN 卷积层硬件实现各类优化的卷积方法 [39,40] .FPGA 在能耗方面更优于 GPU,但浮点运算性能逊于 GPU,因为

目前的 DNN 计算还是重度依赖密集的浮点矩阵乘法(general matrix multiplication,简称 GEMM),而 GEMM 更利

于映射到 GPU 上(常规并行性).

相比通用芯片,专用神经网络加速芯片(TPU,NPU 等)在处理 DNN 计算时能耗更低,性能更高(芯片的面积

和功耗仅为 GPU 的百分之一量级).专用加速器片内主要包括针对 DNN 计算特点而特别设计的运算单元和存

储单元,并且一般会设计专用的复杂指令集(complex instruction set,简称 CISC)来处理复杂的神经元操作,提升

了速度,同时减少了功耗.运算单元有两种主流的结构:(1) 树状结构,包括 DianNao/DaDianNao/PuDianNao

NPU(寒武纪)等;(2) 脉动阵列结构,包括 TPU(Google)、Scaledeep(普渡大学)、Eyeriss(MIT)、ShiDianNao(寒武

纪)、昇腾 Atlas NPU(华为海思)等.存储单元用来存储神经网络每一层的输入值、权重和输出值等参数.随着神

经网络规模变大,传统 2D 存储结构的 DDR 技术已经不能适应高带宽的要求,研究者已开始把最新的 3D 存储