Page 476 - 《软件学报》2025年第8期

P. 476

王昊天 等: MTTorch: 面向 MT-3000 芯片和 Transformer 模型的 PyTorch 算子库实现与优化 3899

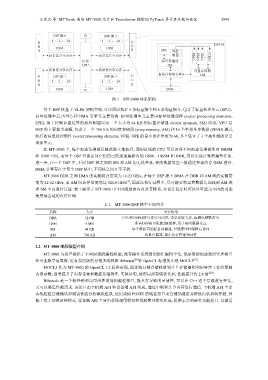

DSP 簇 0 IO DSP 簇 2

1 2 ··· 24 1 2 ··· 24

D D DSP 核

D D

GSM GSM

R R SPE 流控

高带宽共享内存 高带宽共享内存 制器 VPE0 VPE1 VPE2 ··· VPE15

16 核 标量存储器

CPU SM

高带宽共享内存 高带宽共享内存 向量存储器

直接存储器存取 AM

D DSP 簇 1 DSP 簇 3 D

D 1 2 ··· 24 1 2 ··· 24 D

R R

GSM IO GSM DDR

图 1 MT-3000 体系架构

每个 DSP 核基于 VLIW 架构实现, 可以同时执行 5 条标量指令和 6 条向量指令, 包含了标量处理单元 (SPU)、

向量处理单元 (VPU) 和 DMA 引擎等主要结构. 标量处理单元主要由标量处理部件 (scalar processing elements,

SPE), 用于控制向量运算的流控制器以及一个大小为 64 KB 的标量存储器 (scalar memory, SM) 组成. VPU 是

DSP 的主要算力来源, 包含了一个 768 KB 的向量存储器 (array memory, AM) 和 16 个单指令多数据 (SIMD) 模式

执行的向量处理部件 (vector processing elements, VPE). VPE 的最小访存位宽为 64, 其上包含了 3 个高性能的浮点

乘加单元.

在 MT-3000 上, 每个加速集群都是彼此独立地执行, 通用区域的 CPU 可以访问不同加速集群的所有 HBSM

和 DDR 空间, 而每个 DSP 只能访问它们自己的加速集群内的 GSM、HBSM 和 DDR, 用以完成计算密集型任务.

进一步, 在一个 DSP 中, 不同 DSP 核之间的 SM 和 AM 均无法共享, 核间数据交互一般通过共享内存 GSM 进行.

DMA 引擎存在于每个 DSP 核中, 不同核之间互不干扰.

MT-3000 DDR 之间 DMA 的实测访存带宽为 16.22 GB/s, 在每个 DSP 簇上 DMA 在 DDR 和 AM 间的实测带

[3]

宽为 42.62 GB/s, 而 AM 间访存带宽高达 921.6 GB/s , 因此在执行过程中, 尽可能要将运算数据先加载到 AM 或

者 SM 中再进行计算. 表 1 展示了 MT-3000 中不同级别的内存及其特点, 在设计程序时应该尽可能为不同的功能

使用最合适的内存区域.

表 1 MT-3000 DSP 核中不同内存

名称 大小 主要作用

DDR 32 GB CPU和DSP同时可读可写内存, 带宽比较宝贵, 应避免频繁读写

GSM 6 MB 所有DSP核可见的2级缓存, 用于核间数据交互

SM 64 KB 每个核私有的标量存储器, 只能使用控制核心访问

AM 768 KB 向量存储器, 最小访存位宽为64位

2.2 MT-3000 编程模型介绍

MT-3000 为用户提供了不同层级的编程模型, 既有操作系统级别的汇编指令集, 低层级的加速数组管理接口

和专业数学运算库. 也有高层级的异构多线程库 Hthreads [20] 和 OpenCL 标准的实现 MOCL3 [21] .

MOCL3 作为 MT-3000 的 OpenCL 1.2 标准实现, 通过将局部存储映射到片上存储器和利用异步工作组复制

内置函数, 显著提升了内存带宽和数据传输效率. 实验证明, 使用局部存储优化后, 性能提升约 2.8 倍 [20] .

Hthreads 是一个低开销和高可用性的异构编程接口, 既具有足够的灵活性, 可以在 C++ 这个层级进行开发,

又可以满足性能需求. 该接口由主机端 API 和设备端 API 组成, 通过中断和共享内存进行通信. 主机端 API 主要

由线程组管理模块和调试性能分析模块组成, 使用类似 POSIX 的线程接口来管理加速区并降低内核启动开销, 性

能上优于切换时钟模式. 设备端 API 主要由系统调用模块和资源管理模块组成, 提供丰富的硬件功能接口, 以满足