Page 347 - 《软件学报》2021年第12期

P. 347

刘畅 等:RISC-V 指令集架构研究综述 4011

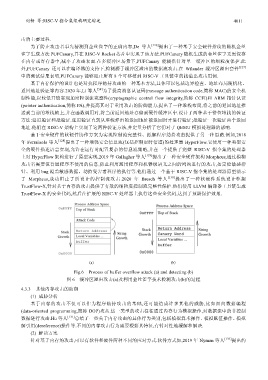

击的主要过程.

为了防止攻击者事先猜测到金丝雀字的正确内容,De 等人 [126] 提出了一种基于安全硬件指纹的随机金丝

雀字生成方法 PUFCanary,并在 RISC-V Rocket 芯片中实现了该方法.PUFCanary 随机生成的金丝雀字无需保存

在内存或寄存器中,减小了攻击表面.在多缓冲区场景下,PUFCanary 能提供针对单一缓冲区的细粒度保护.此

外,PUFCanary 还可以在编译器的支持下,检测源于缓冲区溢出的数据流攻击.在 Wilander 缓冲区溢出套件 [127]

中的测试结果表明,PUFCanary 能够阻止所有 8 个可移植到 RISC-V 工具链中的栈溢出攻击用例.

基于内存保护的设计也是对抗程序劫持攻击的一种基本方法,具体可以包括边界检查、地址布局随机化、

返回地址验证等内容.2020 年,Li 等人 [54] 为了提高消息认证码(message authentication code,简称 MAC)的安全机

制性能,以较低开销实现加密控制流完整性(cryptographic control flow integrity,简称 CCFI)和 ARM 指针认证

(pointer authentication,简称 PA),并提高其对于重用攻击的防御能力,提出了一种堆栈布局,将之前的返回地址推

送到当前的堆栈帧上,并在函数调用时,将当前返回地址存储到硬件缓冲区中.设计了两种基于错位堆栈的验证

方法:延迟验证和批验证.延迟验证直到从堆栈弹出的返回地址被返回时才进行验证;批验证一次验证两个返回

地址.他们在 RISC-V 架构上实现了这两种验证方法,并定量分析了它们对于 QEMU 模拟处理器的影响.

基于安全硬件的软硬件协作方案为实现控制流完整性、抵御程序劫持攻击提供了另一种思路.例如,2018

年 Ferraiuolo 等人 [128] 提出了一种增强安全信息流(包括控制定时信道)的处理器 HyperFlow.它使用一种类型安

全的硬件描述语言实现,允许在运行时配置复杂的信息流策略,并在一个提供了完整 RISC-V 指令集的处理器

上对 HyperFlow 架构进行了原型实现.2019 年 Gallagher 等人 [129] 提出了一种安全硬件架构 Morpheus,通过模糊

攻击者需要但普通程序不使用的信息,防止利用滥用程序和机器级语义之间的鸿沟进行的攻击,如定位敏感指

针、利用 bug 覆盖敏感数据、劫持受害者程序的执行等.他们通过一个基于 RISC-V 指令集的处理器原型演示

了 Morpheus,成功阻止了所设计的控制流攻击.2020 年 Bresch 等人 [130] 提出了一种软硬件系统设计框架

TrustFlow-X,针对基于内存的攻击提供了有效的细粒度控制流完整性保护.他们使用 LLVM 编译器工具链生成

TrustFlow-X 的安全代码,然后在扩展的 RISC-V 处理器上执行这些安全代码,达到了预期保护效果.

(a) (b)

Fig.6 Process of buffer overflow attack (a) and detecting (b)

图 6 缓冲区溢出攻击(a)及利用金丝雀字技术检测攻击(b)的过程

4.3.3 其他内存攻击的防御

(1) 威胁分析

基于内存的攻击不仅可以作为程序劫持攻击的基础,还可能造成许多其他的威胁,比如面向数据编程

(data-oriented programming,简称 DOP)攻击.这一类型的攻击往往通过内存行为模拟操作,对数据流中的非控制

数据进行攻击.Hu 等人 [131] 总结了一些关于内存攻击的具体行为类别,包括模拟算术操作、模拟赋值操作、模拟

解引用(dereference)操作等.不同的内存攻击行为需要根据其特征,有针对性地缓解和解决.

(2) 解决方案

针对基于内存的攻击,可以有软件和硬件两种不同的应对方式.软件方式如,2019 年 Nyman 等人 [132] 提出的