Page 209 - 《软件学报》2020年第10期

P. 209

赵玉文 等:申威 26010 众核处理器上一维 FFT 实现与优化 3185

Key words: Sunway 26010 processor; 1-D FFT; two-layer decomposition; Cooley-Tukey; multi-core parallel

[1]

快速傅里叶变换(fast Fourier transform,简称 FFT)算法被列为“20 世纪十大算法 ”之一,在数字信号处理、

图像处理、微分方程求解和分子动力学等很多学科和科学计算领域具有重要地位.另外,FFT 作为 HPC

[2]

Challenge 基准测试程序的组成部分 ,可以用于评估超级计算机的体系结构和整体性能.

[3]

目前,超级计算机的体系结构已经从多核向众核乃至异构众核发展,“神威·太湖之光” 是世界上首台峰值

运算速度超过 10 亿亿次量级、国内首台采用国产处理器构建的世界第一的超级计算机.截至 2017 年 11 月,已

连续 4 次荣登全球超级计算机 500 强榜首.目前部署在国家超级计算无锡中心,使用的处理器是国产“申威

26010”异构众核处理器.该处理器不同于现有的纯 CPU、CPU-MIC、CPU-GPU 等架构,其采用主-从核架构,单

处理器峰值计算能力为 3TFlops/s,访存带宽为 130GB/s,相比计算能力,其访存能力偏弱.然而,FFT 算法具有计算

密集型和访存密集型的特点,需要根据处理器体系结构的特点设计出适用于此处理器的并行算法和优化策略,

这就给 FFT 的高效实现带来了巨大挑战.

本文根据申威 26010 处理器体系结构的特点,提出了基于两层分解的一维 FFT 众核并行算法.该算法基于

迭代的 Stockham FFT 计算框架,根据 Cooley-Tukey FFT 算法进行分解,将大规模 FFT 分解成一系列的小规模

FFT 来计算.其通过构造合适的任务划分方式,来满足并行度要求和解决负载均衡问题,并采用寄存器通信、访

存计算重叠以及向量化等优化方法进行优化,以有效提高 FFT 的计算性能.

1 申威 26010 处理器

[3]

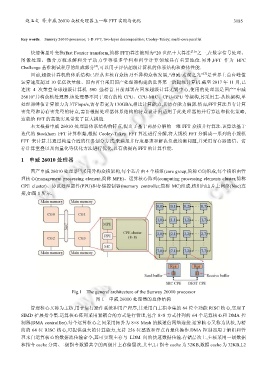

国产申威 26010 处理器 采用异构众核架构,每个芯片由 4 个核组(core group,简称 CG)组成,每个核组由管

理核心(management processing element,简称 MPE)、运算核心阵列(computing processing elements cluster,简称

CPE cluster)、协议处理部件(PPU)和存储控制器(memory controller,简称 MC)组成,核组间由片上网络(Noc)连

接,如图 1 所示.

Fig.1 The general architecture of the Sunway 26010 processor

图 1 申威 26010 处理器的总体结构

管理核心又称为主核,用于运行操作系统和用户程序,其采用自主指令集的 64 位全功能 RISC 核心,实现了

SIMD 扩展指令集.运算核心阵列采用紧耦合的方式进行管理,包含 8×8 方式排列的 64 个运算核心和 DMA 控

制器(DMA controlller).每个运算核心之间采用拓扑为 8×8 Mesh 的簇通信网络连接.运算核心又称为从核,为精

简的 64 位 RISC 核心,可提供强大的计算能力,支持 256 位整数和浮点向量化操作.DMA 控制器用于解析和管

理来自运算核心的数据流传输命令,其可实现主存与 LDM 间的快速数据传输.存储层次上,主核采用一级数据

和指令 cache 分离、二级指令数据共享的两级片上存储层次,其中,L1 指令 cache 为 32KB,数据 cache 为 32KB,L2